■COE拠点形成と研究成果の概要

1.拠点形成計画

1.1 拠点の理念

20年以上、我々はシリコン集積回路技術に重点をおいて研究・教育を進め、挙げてきた世界トップレベルの研究成果を基礎にして本COEを提案した。COEの目的は、将来10年以上、高度情報社会のキーとなるシリコン集積回路技術の本流を進んで、物理理論と情報処理理論に基づく設計原理に立脚して、新しい集積システムの基盤を構築することである。学問における目的はシリコンナノデバイス・回路・アーキテクチャの融合により、高度認識・学習機能を集積化するシステムの基盤技術の構築である。学問としての意義は、現在乖離している情報処理システム・回路設計領域と物質・物理(デバイス・プロセス)領域とを融合した学問分野を構築することである。

最も重要な社会ニーズは情報・電子工学分野でシステムからデバイスを幅広く見通せる専門技術者と、将来リーダとなる人材の育成である。したがって、教育における目的は、先端研究を推進して幅広い視野、思考力と実行力を備えた自立した人材を育成することである。

1.2 COEの目標

(1) 研究目標と技術的独創性

無線通信を導入したシステムは活発に研究されているが、無線をマルチチップ集積システム内に適用すること、これに適した情報処理アルゴリズムと集積アーキテクチャを統合した研究は、他研究機関にはない独創性の高いものである。さらに、光インタコネクトも導入することにより、集積回路の進歩の速度を律してきた経験則である「ムーアの法則」を破る新しい三次元集積技術を狙うものである。

(2) 学問領域形成と育成目標

新しい学問領域は a.物質における電磁波や光の伝播制御、b. アンテナ・デバイス・回路統合集積技術、c.デバイスと超高周波回路統合設計技術、d.光子と電子を融合した超高速情報処理、e.認識・学習処理アルゴリズムとマルチチップ集積との融合技術である。このような学際的な融合領域を形成することにより、次世代をリードする革新的研究とそのための人材育成が可能になる。

教育目標は内外の博士課程の学生を数多く集め、視野の広い博士研究者を輩出することである。具体的には博士課程学生10人/年を目標にする。

(3) 技術的意義と産業における位置づけ

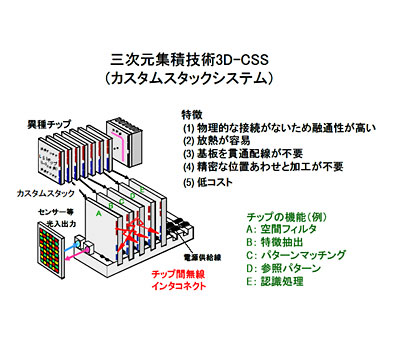

我々のターゲットは異種機能のチップを三次元にスタックして、チップ間を無線で接続した三次元集積システムである。これを3DCSS (three dimensional custom stack system)と呼ぶ。又、光インタコネクトもセンサー間の長距離接続やチップ内の超広帯域接続に用いる。この三次元集積技術と情報処理のアルゴリズムとアーキテクチャを融合させて、大規模集積の限界をブレークスルーする技術を開発する。さらに柔軟性の高いインタコネクト技術により、各チップのデバイスや材料は異種のものでもよいので、柔軟性の高いカスタム化技術として汎用性も高い。

例として三次元集積の画像認識システムを示す。(右図)画像情報の空間フィルタ、特徴抽出、パターンマッチングなど、異種の機能、回路とデバイスを集積化したチップをフレキシブルに集積化できる。

1.3 COEメンバーと研究内容

(1) COE拠点形成の基盤となった世界トップレベルの成果

COEのメンバーは、これまで30年にわたってシリコン集積回路の研究・教育に重点化して、以下の3領域で世界レベルの研究実績をあげてきた。

第1の領域である回路・システムアーキテクチャ領域では、パルス変調方式のアナログデジタル融合回路技術を考案し、画像特徴連想プロセッサを開発して、高性能を実証した。(岩田)機能メモリを研究し、アナログ全並列比較演算回路を考案して、アナデジ融合連想メモリを開発した。また、並列処理システム用のマルチポートメモリ回路を考案し、試作に成功した。(マタウシュ) 光配線を導入した光電子融合集積システムを考案し、世界で始めて画像認識チップをRCNSで学生が試作し、その動作を実証した。(横山)このようにアナログ、メモリの回路・システムを専門とする教員がそろっていることは大きな特徴である。

第2の領域でのデバイスモデリングでは、ドリフト・拡散の物理に基づくMOSトランジスタモデルHiSIMを考案した。(三浦)HiSIMは現在、世界標準のUCバークレイの考案したBSIMモデルに比してパラメータ数が5分の1以下でありながら、モデルの精度が高く、デバイスの微細化を進めた場合の性能予測能力にも優れている。2002年1月からフリーソフトとしてリリースしている。既に主要CADベンダーのシミュレータの標準モデルとして組み込まれています。現在標準となっているBSIMに代わる次世代国際標準を狙っている。

第3領域はナノデバイス・プロセスである。極微細MOSトランジスタを大学の技術と設備で試作することに成功し、信頼性を含む特性の解析評価を行った。(宮崎、角南)30nmゲート長、1.2nmゲート酸化膜厚という微細なデバイスを実際に大学で試作して、その動作を実証したことは、世界の他の大学では全く追随できていないことで、先端企業と並んで世界トップレベルの競争を行っている。集積回路の多層配線システムに関する研究では、低誘電率材料を用いた技術を有しており、さらに電磁波や光を利用したチップの配線技術にも発展させた。(吉川、横山)

1.4 研究内容と担当

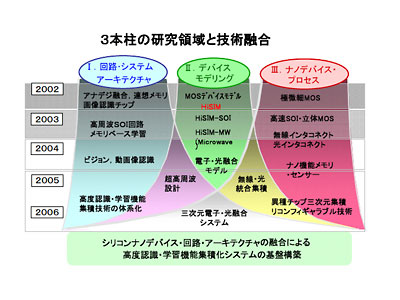

これまでの実績を基礎とする3領域の研究グループを元に、領域融合を進める。

(1) 回路・システム

・MOSデバイスのモデル技術を適用して、高周波・アナログ回路設計技術を高精度化、高信頼化して、三次元集積システムのにおける無線通信回路、高速処理回路設計の基盤として構築する。(岩田、佐々木)

・アナデジ融合高速連想メモリ、学習機能を搭載した連想メモリ、画像分割処理、最小距離演算・探索チップのアーキテクチャとチップ設計、3次元集積動物体認識システム実現に向けた基盤技術を研究・開発する。(マタウシュ、小出)

・高度認識機能の生体情報処理原理に基づく階層的ビジョンアーキテクチャ、マルチオブジェクト認識アルゴリズムとチップアーキテクチャを研究・開発する。(岩田)

(2) デバイスモデリング

・広大オリジナルのHiSIMモデルの適用範囲を高周波動作領域、SOI構造へ拡張し、60nm以下のMOSデバイスのモデルとして世界標準にする。光応答デバイスのモデル化の研究を行う。(三浦)

(3) ナノデバイス・プロセス

・微細化基盤技術 メタルゲートを用いたCMOSデバイス、原子層成長技術をゲート形成技術などの研究開発を行う。(芝原、宮崎、中島)

・微細SOIデバイスとして新しい構造の立体MOSを考案し、構造と製造技術を確立して、試作・評価する。高速・大電流動作回路に適用して、性能向上を図る。(角南、 三浦)

・ナノ機能デバイス、量子ドット形成技術とそれを用いた機能デバイスを研究・開発し、光インタコネクションや情報処理への適用を研究する。 (宮崎、東、村上)

・無線インタコネクト技術 集積化アンテナと広帯域無線回路を研究・開発し、チップ間の無線インタコネクトを用いた三次元集積のキー技術とする。(吉川、佐々木)

・光インタコネクト技術 新しい構造の光スイッチなどの光電集積技術を研究・開発し、三次元集積システムに導入する。(横山、中島)

1.5 拠点形成計画

計画概要は以下の通りである。

2002年 これまで研究成果を継承・発展させ、MOSデバイスとそのモデリングの領域などで共同研究体制を構築する。

2003年 チップ間無線インタコネクションを重点にして、モデリング技術を要にして、デバイスと回路の研究領域の融合を推進する。また、通信理論と集積技術の領域融合のプロジェクトを立ち上げる。この中で、チップ間無線通信の概念を創出し、シミュレーションにより検証する。

2004年 融合領域を拡大して、新概念を実験的に実証して、技術レベルを高める。光インタコネクションと機能メモリを三次元集積システムに導入する方法を考案する。

2005年 無線・光インタコネクション、立体MOSデバイスを集積化する新規の製造技術、設計技術を開拓する。

2006年 基盤研究成果の確立・体系化し、学問領域の形成・確立および教育組織の再編成を達成する。

2. 拠点形成の進捗

2002年度はCOEの研究教育計画の具体化、体制構築、測定装置、評価装置など研究設備整備を行った。

2003年度は、領域融合研究体制を確立し、新概念創出と検証を進めた。

領域を横断テーマとして、高周波MOSデバイスモデルと高周波回路設計、チップ間無線インタコネクトの研究に重点化した。(1) 高周波MOS デバイスとRF回路設計を連携させる研究、(2)超広帯域通信方式と集積化アンテナを整合させる研究を進めた。それにより、集積化アンテナ、インダクタンス結合を用いた無線インタコネクトとそれを用いた三次元集積カスタムスタックシステム:3DCSS)の基本構成概念を考案し、特許出願した。

また、生体処理原理による画像処理を実現するための無線インタコネクションを用いたアーキテクチャの研究を進めた。連想メモリによる画像処理、さらに、三次元集積システムを実現するための新しいデバイス立体MOSデバイスと材料・プロセス技術も進捗させた。

COEの概念、成果を情報発信するために2003年3月に第1回の国際ワークショップを開催した。また、2004年1月にはデバイスモデルをテーマとした第2回ワークショップを開催した。

2003年にはCOEの研究テーマとして、「高い認識能力をもつシステムのためのチップ間無線インタコネクトを用いた三次元集積アーキテクチャ」が文科省科学技術研究補助金基盤研究(S)に採択され、また、基盤研究(A)2件が採択された。COEメンバーは多数の公的研究機関の国家プロジェクト、民間企業との共同研究を進めている。

2.1 研究領域融合と研究体制

HiSIMモデルをマイクロウエーブ領域、さらに光・電子融合デバイスモデルに拡張する。これを研究領域融合のための要として、回路・システム領域とデバイス・プロセス領域を融合させて、新概念を生み出し、それを基盤技術とする世界的な研究拠点を形成する。

(1)デバイスと回路設計の融合 高周波MOSデバイスHiSIMモデルを高精度化し、10GHz帯のRF回路の設計に適用して、デバイス構造、デバイス性能、回路構成、回路性能を統合した設計技術を確立する。広帯域無線インタコネクトを低電力で実現する。

(2)先端集積技術と通信技術の融合 チップ間無線インタコネクトを実現するために、シリコン中の電磁波伝播、集積化アンテナ、UWB通信方式CMOS送受信回路の研究開発を進めた。

(3)テラビット情報処理システムとして、以下のアルゴリズムを研究し、高度な認識・学習機能を集積化する三次元集積アーキテクチャを提案する。(i)生体処理に基づく階層的特徴分析抽出機能を持ったビジョンシステム、分析情報を統合して再構成、認識するアルゴリズム、(ii)連想メモリベース学習、デジタル画像処理、動画像認識アルゴリズムを研究開発する。

(4)デバイス・プロセスでは、微細化基盤技術をデバイスに立体MOSトランジスタに適用する。

光インタコネクトのための光デバイスの構造、製造とモデリング技術を融合して新構造を提案する。

ナノメータ量子構造を導入した機能メモリやセンサーの研究を展開し、無線・光統合三次元集積技術の基盤を固める。

2.2 若手研究員を核とする研究領域融合研究体制の構築

2003年度はポスドクCOE研究者を公募して、外国人3名を含む9名を採用し、領域の境界に位置するテーマを担当させて、研究領域融合研究体制を構築した。(図参照)

2004年にはポスドク研究員を15名、博士課程学生研究員を16名に増加する計画である。

COE研究員のテーマを境界領域に設定することにより、ボトムアップの共同研究を推進した。また、COE研究員全員による討論、交流の場を設け、自由な発想による研究協力を推奨して、研究領域融合を進めた。

2.3 大学院教育組織の構築

先端研究に直結した実践的な大学院教育の充実により、有能な博士研究者を育成して、次世代のリーダとすることがCOEの重要な目的である。COEの理念に基づく教育を実践するために、先端物質科学研究科に半導体集積科学専攻を2004年4月に発足させた。広い分野の技術力、広い視野の洞察力を習得できるように教育する。また、学生の資質や能力向上のために、自立した研究企画・立案をさせることにより思考力、企画力を養うなど、教育方法にも工夫している。

博士課程前期では半導体集積科学のカリキュラムを編成し、実施している。世界水準の実証的な研究を通して、まず高度な知識と技術を養う。また、学生の知識の幅と視野を広げるために、スーパクリーンルームの製造装置とLSI設計・テストシステムを活用した非専門分野での演習・実習科目を実施している。さらに、企業でのインターンシップに関して、研修内容・指導体制の事前検討、研修成果の厳格な評価に基づいて単位を与えるルールを設けて、試行している。これらに学生が積極的に取り組む意欲が高まっている。

博士課程後期については、将来のリーダーとなりうる質の高い学生を育成するために、COEの目的を達成するためのテーマを担当させる。COE推進者による複数教員による指導を有効なものにして、学生の独創性、自主性を高める。博士課程後期の学生の数がCOEの拠点形成とともに2倍以上に増え、学生の受賞も増加傾向にあり、質の向上を達成することができた。

3.研究成果概要

3.1 研究成果と新知見

(1) 高周波デバイスモデル

・60nm以降のMOSデバイスの回路設計用モデルの開発およびRF回路で問題を生じる熱雑音の測定技術を確立し雑音をモデル化した。モデルはパラメータを使わないで熱雑音を予測でき、困難な測定を不要化した。

・国際標準MOSデバイスモデルを決定するためのコンンパクトモデルカウンシル(CMC)で、次世代国際標準の候補に選ばれた。

・0.18umCMOSデバイスとVCOを搭載したテストチップを設計、評価して、RF回路設計の高精度化を図った。

・シリコンに集積化できる受光デバイスの回路シミュレーションモデルの基本概念を開発した。この光応答モデルでは、非定常輸送効果考慮の必要性を明確化した。

(2) 3次元集積のための無線インタコネクトの基盤技術

・チップ間グローバル無線通信の基本素子となるSi上ダイポールアンテナを用いて、 抵抗率10ΩcmのSi基板中を20GHzの電波が、損失2dB/mmで伝送できることを初めて実証した。さらに、基板抵抗率を上昇させることにより、伝送損失を20dB低減することに成功した。

・高周波広帯域回路 UWBトランシーバを0.18ミクロンCMOSデバイスを用い、デジタル回路主体で設計し、帯域約3GHzで50Mbpsのデータレートを得た。これらにより、チップ間の無線通信これによりチップ間無線インタコネクをシステムクロックやデータ転送に用いた三次元集積の可能性を示した。

・隣接チップ間ローカル無線インタコネクト実現のために、Si上インダクタの共振を利用した送受信回路方式を考案し、 ビットレート3Gb/s以上で消費電力9mW(従来の1/10)の見通しを得た。(特許出願)ギガビット/秒のデータ転送が低電力で実現でき、チップ間で並列に多ャネルの接続を実現できる。これは二次元の画像情報をそのままチップ間で転送できるので、生体的ビジョンシステムを三次元集積する可能性を示した。

(3) 連想メモリと認識学習システム

・短期・長期記憶の概念を実現した連想メモリベース自動学習アーキテクチャを開発した。

・高速(< 300ns)、小面積(140um2)、低消費電力(2mW/pattern)の最小距離検索連想メモリ、および低消費電力な画像分割処理を導入した画像分割アーキテクチャの設計とチップ試作を行った。

(4) 高認知度システムアーキテクチャ・アルゴリズム

・ローカルおよびグローバル無線インタコネトを用いたマルチチップ処理階層アーキテクチャを考案した。

・主成分分析によるマルチオブジェクト認識のアルゴリズムの評価、マルチオブジェクト認識への適用性を得た。

(5) 集積デバイス基盤技術

・レーザアニールを用いた残留欠陥の無い深さ10nmの浅接合形成技術を達成した。

・メタルゲートMOS構造において、ゲート絶縁膜の上方界面のみに窒素のパイルアップを形成して、仕事関数を制御できることを示した。

・高誘電率ゲート絶縁膜材料としてSi窒化膜、ジルコニウム酸化膜およびそれらの積層構造の原子層成長法について研究し、リーク電流の低減、信頼性の向上等を実現した。

(6) 立体MOSデバイス

・バルクSiにおいて新しい素子分離法、および高さ1μm、幅54nmのSiビーム(梁)でチャネル長2μmの立体トランジスタを初めて実現した。さらに、シリコンオンインシュレータ(SOI)を用いて、高さ1μm、幅40nmのSiビーム(梁)でチャネル長0.2μmの立体トランジスタを実現した。これは従来のFINFETに比べ平面面積効率が20倍高い。

(7) 光電子融合 光インタコネクト (チップ内光配線技術は光電子融合システムのために必須な基盤技術)

・コンパクト(分岐部サイズ〜10μm)で分岐特性の良好な積層型分岐光導波路の設計・製作技術を開発した。

・感光性絶縁膜を用いて約半分の工程数で3次元フォトニック結晶構造を形成する方法を開発した。(特許出願)

(8) 量子機能デバイス (ナノ機能メモリ・センサは電子・光融合を実現する基盤技術)

・Si量子ドットを浮遊ゲートとするMOSトランジスタにおいて量子ドットへの多段階電子注入に起因する閾値電圧の段階的シフトの観測に成功した。

・量子ドット間における電荷の再分布が電子の注入に重要な役割を果すことを実験的に明確化した。

・Geコア/Siクラッド構造の量子ドット作製プロセスの確立に成功した。

3.2 今後の方針

領域融合によりチップ間無線インタコネクトの新概念の創出ができた。これを核にして、到達目標を明確にして、理論的モデル・シミュレーションによる研究と、プロトタイプの設計、試作を通した実験的な研究を進めて、概念の具体化、検証を進めて、基盤技術として確立する。また、この先端的研究を通して、多くの博士研究者を養成する。

|