# 新構造トランジスタと集積化技術

処理能力向上: デバイスの高速化 周波数特性向上 面積当たりの駆動電流, drive 増大

多様化する高速·低消費電力デバイス 微細プロセスコア技術

# テラ情報処理のための新構造トランジスタ

### (1)集積デバイス基盤技術

- ·デュアルメタルゲート 仕事関数制御

- ・極浅ソース・ドレインによる 短チャネル効果抑制

- ·原子層成長high-k絶縁膜と 原子層成長Si窒化膜の スタック構造のゲート絶縁膜

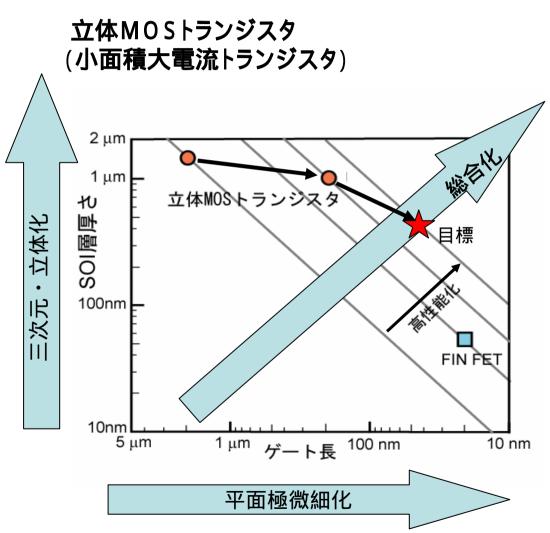

### (2)三次元立体MOSデバイス

・小面積でゲート幅Wを拡大て、 面積当たりの電流増大 電力制御回路に適用 しきい値制御 **減小抑制**

**I**drive

増大

增大:10倍以上

$\mu$  : キャリヤ易動度

ε: ゲート絶縁膜厚誘電率

W:ゲート幅

L : ゲート長

t: ゲート絶縁膜厚

# デバイス・プロセス研究課題の相互関連

無線あるいは光による三次元配線 モデリングによる性能予測 量子ドット立体集積構造 (多値不揮発性メモリ 超高感度光検出器など)

> ALD high-kゲート絶縁膜 ALD窒化ゲート絶縁膜 デュアルメタルゲート 極浅ソース・ドレイン 直接パターニングLow-k膜

## 新構造デバイス・微細化基盤技術

- 1.三次元 ビームチャネルトランジスタ(Beam Channel Transistor)

- · with high current driving capability aiming at applications to power control with small chip area.

- 2. 仕事関数制御 NiSi ゲート MOSデバイス

- NiSi workfunction tuning method by Sb pre-doping to poly-Si before silicidation

- 3. High-k 絶緣膜形成 原子層成長(ALD)技術

- · Si-nitride/SiO2 stack gate dielectrics for future scaled DRAMs.

- Enhanced reliability in NBTI was achieved.

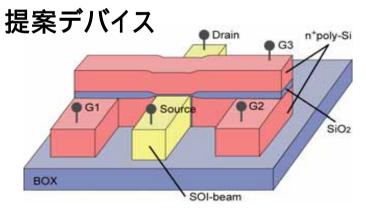

# 立体3並列ゲートトランジスタの提案

VLSI回路における 消費電力の問題

個々のデバイス特性制御 による最適化の重要性

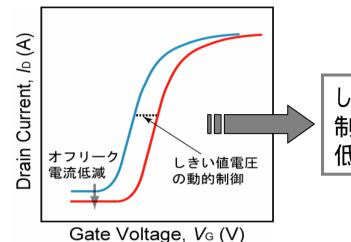

しきい値電圧の動的 制御による待機電力 低減効果

SOIビームに独立した三つ のゲート電極を形成

各ゲートに独立に電圧を印可

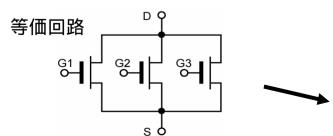

単一MOSFET

基板バイアスによる デバイス特性の動的制御

三並列MOSFET

回路面積の縮小

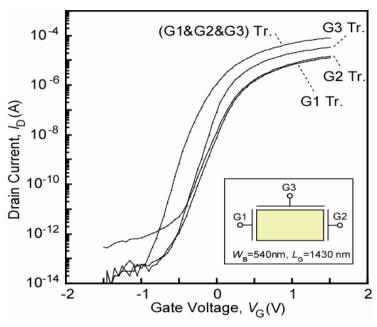

# 立体3並列ゲートトランジスタの試作に成功

#### 各ゲートによる電流 制御動作を確認

( 非動作ゲートの 印可電圧を-1Vに固定)

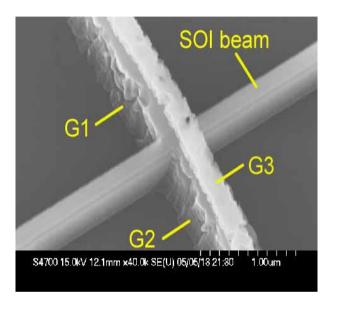

#### 試作デバイスのSEM像

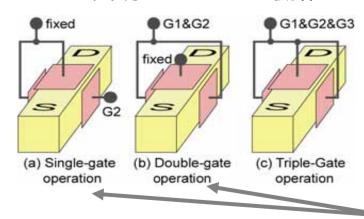

独立ゲートにより実現される三つの動作モード

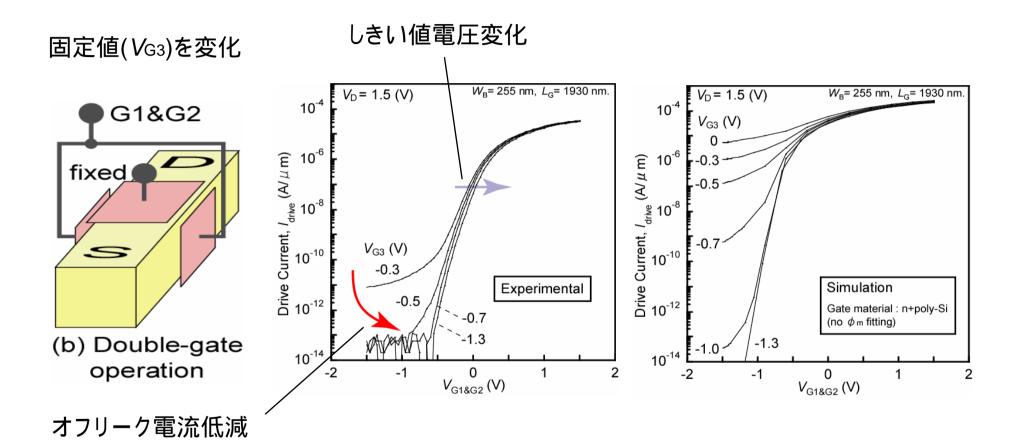

固定値の印可電圧を変えることによる デバイス特性の制御

## ダブルゲート動作におけるデバイス特性制御

デバイスシミュレーション\*より期待される オフリーク電流低減効果,しきい値電圧変動を確認

## 新構造デバイス・微細化基盤技術

- 1.三次元 ビームチャネルトランジスタ(Beam Channel Transistor)

- with high current driving capability

aiming at applications to power control with small chip area.

- 2. 仕事関数制御 NiSi ゲート MOSデバイス

- NiSi workfunction tuning method by Sb pre-doping to poly-Si before silicidation

- 3. High-k 絶緣膜形成 原子層成長(ALD)技術

- · Si-nitride/SiO2 stack gate dielectrics for future scaled DRAMs.

- Enhanced reliability in NBTI was achieved.

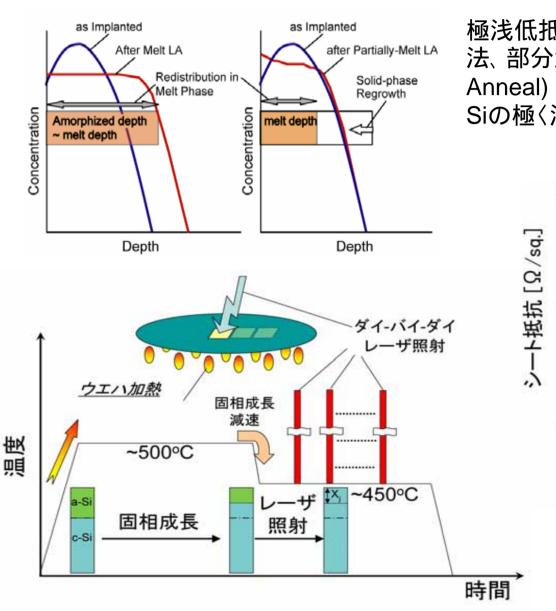

### 部分溶融レーザアニール(PMLA)法の提案

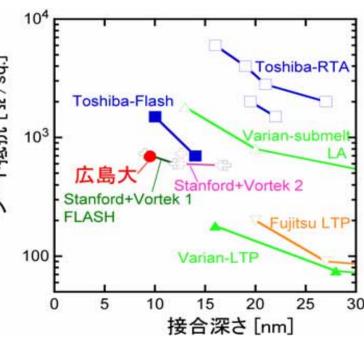

極浅低抵抗接合形成に適した新しいレーザアニール法、部分溶融レーザアニール法(Partial Melt Laser Anneal) を提案。低温固相成長を組み合わせることで、Siの極く浅い表面付近のみを溶融させることが特徴。

シート抵抗と接合深さのベンチマークで世界最高水準を達成。

国際会議招待講演2回([10,18])

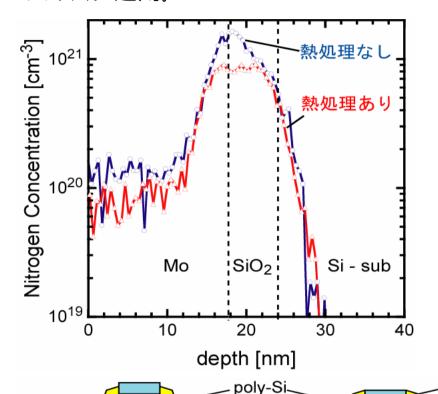

### CMOSデバイスのためのMoゲート仕事関数変調の研究

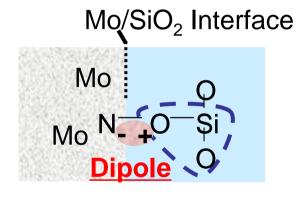

Mo上に堆積させたTiNからNを固相拡散させMoの仕事関数変調 させる手法を初めてデバイスに適用。

Silicide

p-MOS

仕事関数大

TiN

n-MOS

仕事関数小

Mo ·

仕事関数変調が界面にパイルアップしたNによることを明らかに(左上図青線)。→ 電気陰性度差に基づく双極子形成モデルを提案。 国際会議[8]で発表

しかし、Nのパイルアップがデバイス製作時の 熱処理中に減少する問題を発見(左上図赤線)

→ 対策プロセス・デバイス構造を提案

(日·米 特許出願済、国際会議[16]で発表、 2006年4月国際会議招待講演予定)

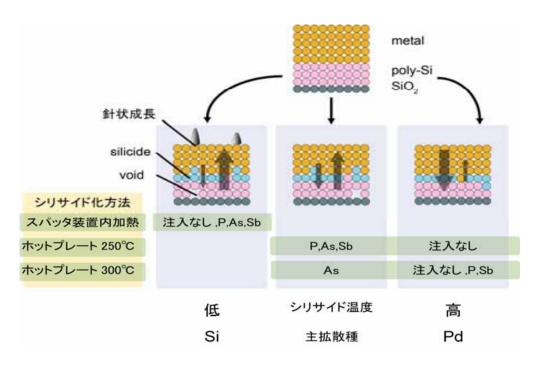

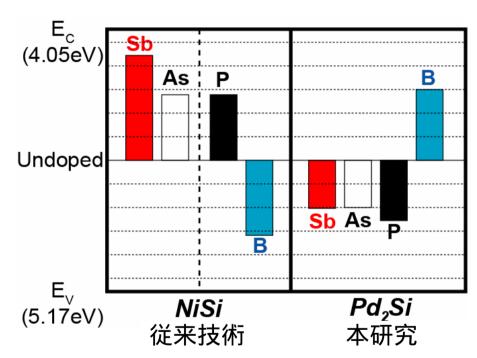

## 新しいメタルゲート材料Pd<sub>2</sub>Siの研究

次世代のMOSデバイスへの採用が期待されているフルシリサイドゲート構造(現在のポリションをシリサイドで置き換える構造)のための新しい材料を研究。Pd2Siは従来のNiSiに比べ、低温で形成可能であり、且つ低ストレスという特長を有す。

良質のPd2Si膜を得るためには、シリサイド化時のSiの拡散を抑えることが重要であることを解明。国際会議[22]で発表。

不純物導入による仕事関数変調が従来のNiSi と同等程度可能であることを実証。(国際会議 投稿中)

21世紀COE最終年度はMOSFETへ適用し素子性能を評価予定。

## 新構造デバイス・微細化基盤技術

- 1.三次元 ビームチャネルトランジスタ(Beam Channel Transistor)

- · with high current driving capability aiming at applications to power control with small chip area.

- 2. 仕事関数制御 NiSi ゲート MOSデバイス

- NiSi workfunction tuning method by Sb pre-doping to poly-Si before silicidation

- 3. High-k 絶緣膜形成 原子層成長(ALD)技術

- · Si-nitride/SiO2 stack gate dielectrics for future scaled DRAMs.

- · Enhanced reliability in NBTI was achieved.

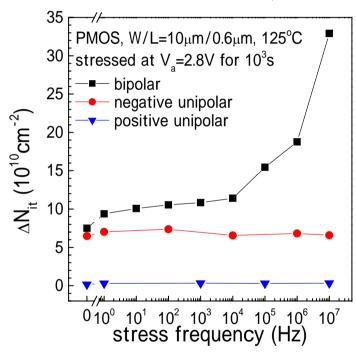

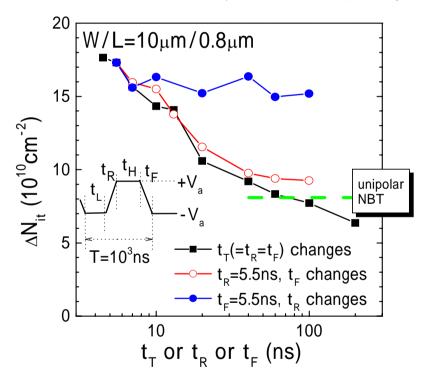

### 微細MOSのための高信頼性ゲート絶縁膜の開発

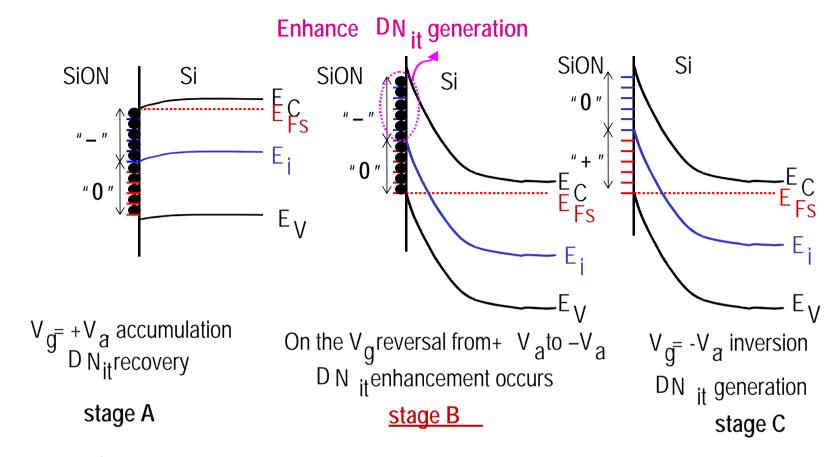

ダイナミックバイポーラパルスストレスによる窒化酸化膜ゲート絶縁膜における界面トラップ生成

微細MOSFET適用のために、SiONゲート絶縁膜の信頼性を調べ、新知見を得た。

プラズマ窒化酸化膜ゲート絶縁膜を用いた pMOSFETのダイナミック電圧ストレス下 界面トラップ生成量。

10<sup>4</sup> Hz以上の周波数領域において、周波数の増加に伴う界面トラップの急激な増加が観測

界面トラップ生成量に対するバイポーラパルス電圧ストレスの立ち上がり・立下り時間依存性。 界面トラップ生成量は、立下り時間にのみ依存

- ・高周波バイポーラストレスにおける著しい界面トラップの増加は、界面におけるトラップ電子が ゲート電圧Vg の急激な正から負への変化に追随できない事により生じる。

- ・追随できない電子は過渡的にゲート電界と同じ向きの内蔵電界を作りSi-H ボンドの解離を促す。

IEEE Electron Device Letters, Vol. 26, No.3, pp. 216-218 (2005)

IEEE Electron Device Letters, Vol. 26, No.6, pp. 387-389 (2005)

IEEE Electron Device Letters, Vol. 26, No.9, pp. 658-660 (2005)