# Multiple-Step Electron Charging in Si Quantum-Dot Floating Gate nMOSFETs

Mitsuhisa Ikeda, Yusuke Shimizu, Taku Shibaguchi, Hideki Murakami and Seiichi Miyazaki

Department of Electrical Engineering, Graduate School of Advanced Sciences of Matter, Hiroshima University, Kagamiyama 1-3-1, Higashi-Hiroshima 739-8530 Phone: +81-824-24-7648, FAX: +81-824-24-7038, E-mail: semicon@hiroshima-u.ac.jp

#### 1. Introduction

The application of silicon quantum dots (Si-QDs) to a floating gate of MOSFETs has been attracting much attention because of its multivalued capability at room temperature [1, 2]. For MOS structures with a Si-QDs floating gate [3-5], we have confirmed the memory operations at room temperature. Also, we have demonstrated unique multiple-step charging in the Si-QD floating gate [4, 5], and suggested that the multiple-step electron charging of Si-QDs is caused by the Coulomb blockade at QDs and from neighboring charged QDs.

In this paper, we report the temperature dependent charge injections to the Si-QDs floating gate in nMOSFETs and discuss a possible mechanism for the multiple-step charging.

### 2. Fabrication of Si-QDs Floating Gate MOSFETs

Hemispherical and single-crystalline Si-QDs were self-assembled on a 3.3nm-thick SiO<sub>2</sub> by controlling the early stages of LPCVD of pure SiH<sub>4</sub> at 575°C [6]. After the formation of the first Si-QD layer, a ~1nm-thick thermal oxide layer was grown at 850°C in 2%O<sub>2</sub> diluted with N<sub>2</sub>, and the second Si-QD layer was deposited under the same conditions. The average dot height and the total dot density evaluated by AFM were ~7.2nm and ~6x10<sup>11</sup> cm<sup>-2</sup>, respectively. The surface of the second Si-QD layer was also covered with a ~1nm-thick thermal oxide. Subsequently, a 3.3nm-thick amorphous Si layer was grown over the dot layer by LPCVD of 10%Si<sub>2</sub>H<sub>6</sub> diluted with He at 440 °C, and fully oxidized in dry O<sub>2</sub> at 1000 °C to form a 7.5nm-thick control oxide. Finally, n<sup>+</sup>poly-Si gate and source/drain junction were fabricated. The gate length and width are 0.8 and 10µm, respectively.

# 3. Results and Discussion

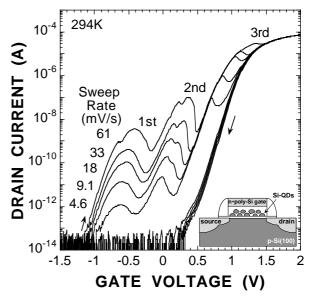

The drain current versus gate voltage (I<sub>D</sub>-V<sub>G</sub>) characteristics of a Si-QDs floating gate MOSFET were measured at room temperature as shown in Fig. 1. The gate voltage was swept between -4 and +3V at a different sweep rate with a range of 4.6 to 61mV/s. The I<sub>D</sub>-V<sub>G</sub> curves show characteristic hysteresis arising from electron charging or discharging of the Si-QDs floating gate. Distinct current bumps, which were observed in the gate voltage sweeping from -4 to +3V, indicate the multiple-step electron charging to the Si-QDs floating gate caused by the Coulomb blockade effect. Considering that, in the region of 0-0.5V, a new current component emerges with increasing sweep rate, four steps of electron injection to the Si-QDs floating gate with an areal dot density of ~6x10<sup>11</sup> cm<sup>-2</sup> are confirmed. In addition, the threshold voltage shift at each charging steps is not equal to that of the next charging step and slightly increased with progressive electron charging. This implies that the Coulomb

Fig. 1 Drain current vs gate voltage characteristics of a Si-QDs floating gate MOSFET, which were measured after fully discharged at a gate bias of -4V. The drain voltage was 50mV. The voltage sweep rate was changed in the range from 4.6 to 61 mV/s. A cross-sectional view of a Si-QDs floating gate MOSFET is illustrated in the inset.

interaction from the neighboring charged QDs plays a subsidiary role on the electron tunneling from the channel to the Si-QDs. In other words, this can be interpreted in terms that the charging energy of the Si-QDs depends on not only charged states of individual Si-QDs but also charged states of neighboring QDs. In general, since the charging time of the Si-QD floating gate strongly depends on the gate voltage, faster the sweep rate is, higher the gate voltage for the charge injection becomes. In fact, with increasing sweep rate, the current bumps appear at higher gate voltage. Besides, the result of Fig. 1 implies that the charging voltage is affected by the redistribution of electrons in the Si-QDs floating gate during the gate voltage sweep as discussed later.

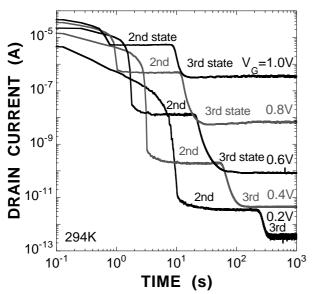

Figure 2 shows temporal change in the drain current ( $I_D$ -t) measured at constant gate biases after complete discharging of the Si-QDs floating gate. The drain current decreases stepwise with time due to the electron charging to the Si-QDs floating gate. The threshold voltage after each current step corresponds to that of the scanned  $I_D$ -V $_G$  characteristics. The distinct metastable states, in which the drain current is almost constant with respect to holding time, indicate that the total amount of effective charge in the Si-QDs floating gate remains unchanged in each of the metastable states. This result suggests that electrons injected in the Si-

Fig. 2 Temporal change in drain current at various gate biases and a drain voltage of 50mV after complete discharging of a Si-QDs floating gate. For the discharging, the gate was biased at -4V.

QDs floating gate redistribute during each metastable state to reduce the effect of the Coulomb interaction among the charged QDs, namely to decrease the charging energy of QDs.

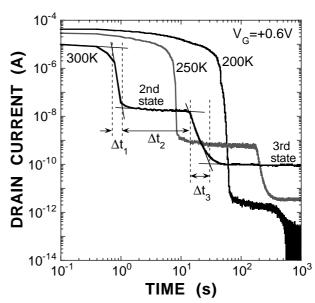

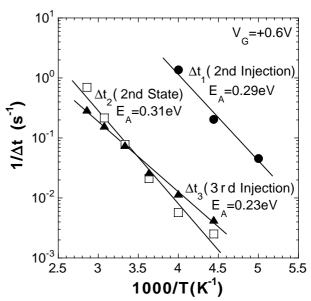

To get a clear insight on the mechanism of electron charging to the Si-QDs floating gate, temperature dependence of I<sub>D</sub>-t characteristics was measured in the temperature range of 200-300 K at a fixed gate bias as shown in Fig. 3. Obviously, a decrease in temperature decelerates the electron charging and prolongs the metastable states. This suggests that the tunneling probability is increased with temperature for redistribution of electrons in the Si-QDs floating gate. The charging time ( $\Delta t_1$  and  $\Delta t_3$ ) and metastable time ( $\Delta t_2$ ) were determined with the method in which both charging and metastable states were linearly extrapolated as illustrated in Fig. 3, and their reciprocal values are summarized in Arrehnius plots (Fig. 4). The activation energy in the range of 0.23~0.31eV were obtained from the slopes of the Arrehnius plots. When estimating the sum of quantized and charging energies for QDs, we found that the obtained activation energy is almost equal to the energy separation between states for tunneling in QDs. Therefore, we suggest that the electron tunneling between different energy states plays an important role on the observed multiple-step charging characteristics.

## 4. Conclusions

The multiple-step electron charging to a Si-QDs floating gate in the MOSFETs has been studied in the temperature range of 200-300K. The metastable states in electron charging at the constant gate bias are attributable to the redistribution of electrons in the Si-QDs floating gate. The Coulomb interaction among the neighboring charged dots may play an important role in regulation of the electron injections to the Si-QDs floating gate and the generation of intermediate charged states in which the redistribution of electrons in the floating gate proceeds without increasing charges by electron tunneling between the different energy states in the neighboring dot.

Fig. 3 Temperature dependence of  $I_{D^{\text{-}}}t$  characteristics at a gate bias of 0.6V after complete discharging under the same condition of Figs. 1 and 2. The drain voltage was 50mV. The definition of the characteristic times ( $\Delta t_1$ ,  $\Delta t_2$  and  $\Delta t_3$ ) is demonstrated in the curve at 300K.

Fig. 4 Arrehnius plot of 2nd injection ( $\Delta t_1$ ), 2nd state ( $\Delta t_2$ ) and 3rd injection ( $\Delta t_3$ ) time from  $I_D$ -t characteristics.

# References

- S. Tiwari, F. Rana, K. Chan, L. Shi and H. Hanafi, Appl. Phys. Lett. 69 (1996) 1232.

- [2] L. Guo, E. Leobandung and Y. Chou, Appl. Phys. Lett. 70 (1997) 850.

- [3] A. Kohno, H. Murakami, M. Ikeda, H. Nishiyama, S. Miyazaki and M. Hirose, Ext. Abst. of the 1998 Intern. Conf. on Solid State Devices and Materials (Hiroshima, 1998) 174.

- [4] A. Kohno, H. Murakami, M. Ikeda, S. Miyazaki and M. Hirose, Jpn. J. Appl. Phys. 40 (2001) L721.

- [5] M. Ikeda, Y. Shimizu, H. Murakami and S. Miyazaki, Jpn. J. Appl. Phys. 42 (2003) to be published.

- [6] S. Miyazaki, Y. Hamamoto, E. Yoshida, M. Ikeda and M. Hirose, Thin Solid Films, 369 (2000) 55.