## **Recent Progress of the COE**

#### Atsushi Iwata

Graduate School of Advanced Sciences of Matter, Research Center for Nanodevices and Systems, Hiroshima University 1-3-1, Kagamiyama, Higashi-Hiroshima, JAPAN 8739-8526, iwa@dsl.hiroshima-u.ac.jp

## 1. Target of the COE

The features of the COE on "Nano-electronics for Tera-bit Information Processing" are to fuse the 3 research fields of (1) circuit design and system architecture, (2) device molding, and (3) nano-devices and processing. Research efforts cover next generation nanodevice technologies collaborated with device modeling, high performance circuit design and architecture for high performance system. Our targets are to realize three dimensional integration utilizing inter-chip wireless interconnects and on-chip optical interconnects, (Fig.1) and to demonstrate its feasibility by implementing multi- and moving-object recognition systems for hyper robot brains.

#### 2. Research Fields and Subjects

Device modeling is a key to organize research collaboration between the field of circuit/system and device/process. RF circuit design utilizing the advanced device model realizes the wireless interconnects with low power dissipation. In the device field, for realizing tera-bit processing, new MOS devices, RF transceiver with integrated antennas, and integrated optical components has been studied. Research on multi-layered Si quantum dot structure will results in new optical sensor and memory devices. Synthesizing these bases, we are aiming innovative 3D integration technologies and system applications.

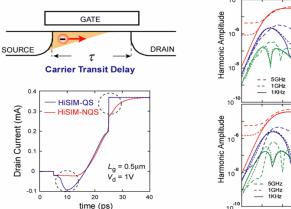

#### 4. Major Achievements 4.1 MOSFET Model:

**HiSIM** model has been developed for ultimately scaled MOSFETs. Its concept is to describe devices utilizing surface potential, based on physical principles of drift and diffusion. *HiSIM2-NQS* including Non-Quasi-Static effects realizes sufficient accuracy in GHz and Gbit/s circuit operation. (Fig. 2) The Compact Model Council selected *HiSIM* as the final stage candidate for the standard model with *PSP* model proposed by Penn. State University and Philips in March, 2005. The HiSIM Research Center has been established in Hiroshima University in June, 2005, and now supporting the final evaluation by affiliations over the world for standardizing at the end of 2005. Moreover, the new techniques have been investigated for modeling of sensitivity to photons and electromagnetic wave.

#### 4.2 Wireless Interconnection

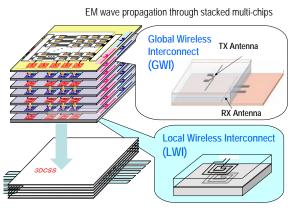

## [Wireless interconnects using on-chip antennas]

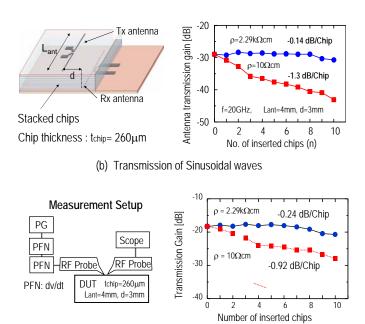

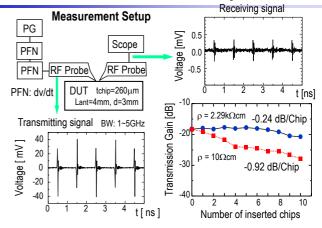

A new inter-chip and intra-chip connection technique using radio wave propagation using on-chip dipole antennas was proposed. We have confirmed by measurements that antenna transmission gain is about -28dB at 20GHz, and it decreases 0.14dB/chip with 270 $\mu$ m chip thickness. (Fig.3) UWB transmitter and receiver chips have designed with a 0.18 $\mu$ m CMOS. By measurement of the test chips, generation and receiving of UWB pulse were confirmed. We call this technique Global Wireless Interconnection (*GWI*) which is applicable to clock distribution and wide bandwidth busses.

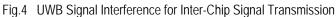

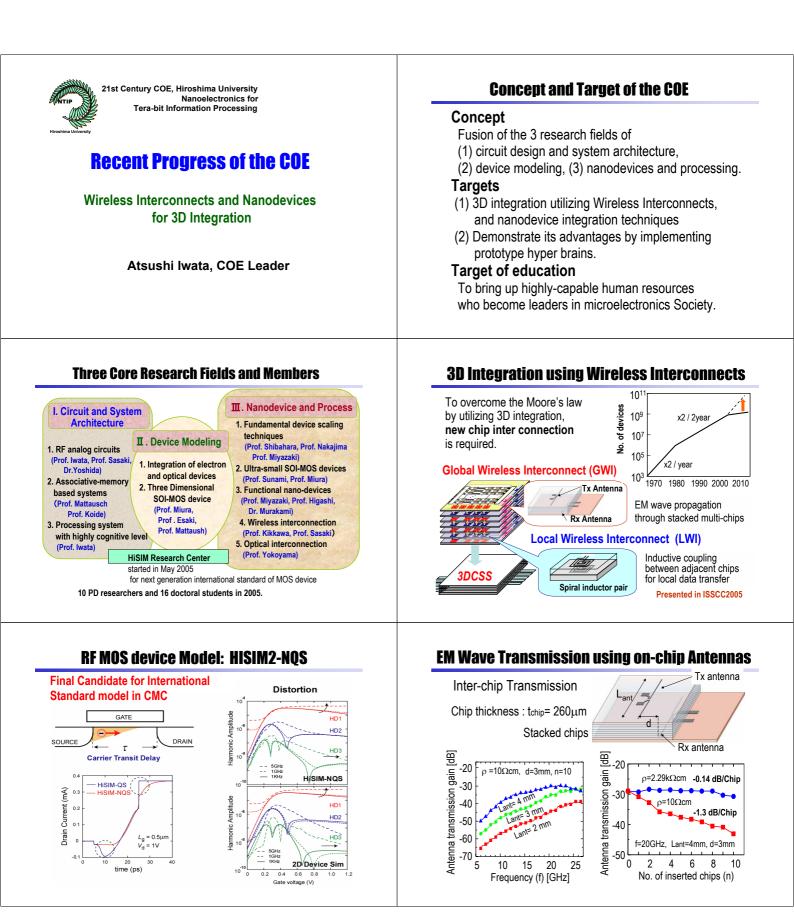

Received UWB signal was interfered by DC noise as well as distorted rectangular wave noise. Differential mode operation could eliminate the digital noise in the lower frequency range. However, digital noises with the spectrum above 5GHz could not be removed. High pass filter above 5.1 GHz could suppress the digital noise interference and recover the UWB signal. Bit error rate (BER) was degraded by increasing noise voltage, but improved by increasing the resistivity of the Si substrate. BER of the antenna with 4 mm long was the lowest because the transmission loss of interference signal became maximum. (Fig.4)

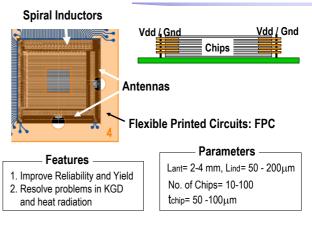

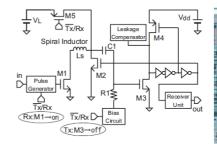

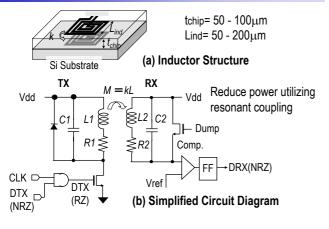

#### [Wireless interconnects using on-chip spiral inductors]

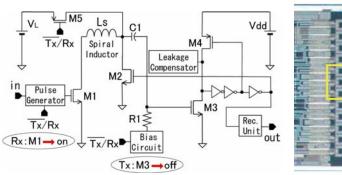

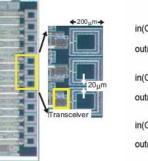

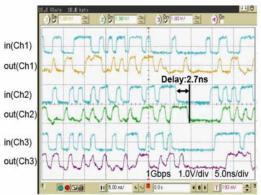

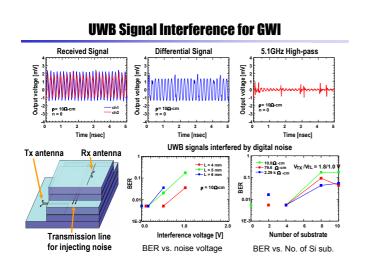

Wireless interconnection using on-chip spiral inductor pair was proposed for inter-stacked chip connection. Resonation phenomena of inductor pair are utilized for reducing dissipation power and increasing bit rate with a simple transmitter and receiver. (Fig.5). In order to replace via-holes used in 3D stacked chips, an asynchronous scheme is necessary as well as a source synchronous system. The asynchronous scheme was realized with double pulse coding and a self-biased detector.

We have designed and fabricated a test chip with 12 channels using 0.18 $\mu$ mCMOS. Power dissipation was reduced to 0.95mW per 1Gps. Bit error rate of 10<sup>-10</sup> was attained with relaxed alignment of 20 $\mu$ m (Fig.6)<sup>[2]</sup>

The inductive coupled interconnection is applicable to parallel data transfer at arbitral points of chip. We call it Local Wireless Interconnection (LWI).

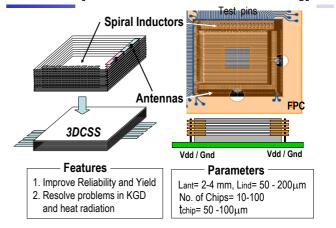

# 4.3 Concept of 3D integration using wireless technologies

3D integration using *GWI* and *LWI* called 3-dimensional custom stack system (*3DCSS*) was proposed<sup>-[1]</sup> Alignment accuracy of stacked chips is relaxed as low as about a half of the inductor size. The distinguished feature of *3DCSS* is to implement a customized system composed of various kinds of chips with multi functions and devices, with an on-chip standard wireless interconnect interface. Yield and Known Good Die (KGD) problems are also resolved by chip testing using wireless pads.

In order to verify inter-chip data transfer concept of 3DCSS, an experimental setup which consists of LWI test

Inductive coupling for local data transfer

# Fig. 1 3-dimentional Custom Stack System (3DCSS) utilizing Wireless Interconnections

(b) Transmission of Gaussian Monocycle Pulses

Fig. 3 Radio Wave Transmission through Si Chips Measured Transmission Loss using on-chip antennas

Fig. 2 MOS device Model (HiSIM2-NQS)

Fig. 5 LWI Transceiver and its test chip

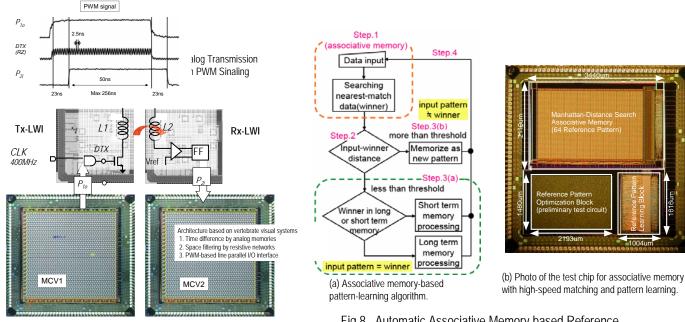

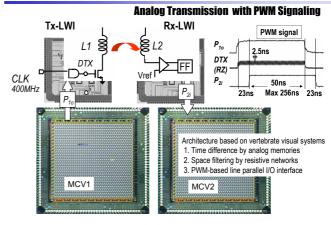

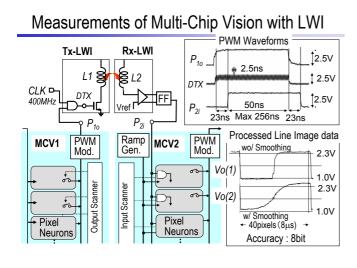

chips and vision chips was made. A multi-chip vision (MCV) based on hierarchical biological processing with a PWM-based line parallel I/O interface are implemented with a 0.35 $\mu$ m CMOS technology which consist of neurons, a resistive network for horizontal connection. Two chips, MCV1 and MCV2 are connected by two LWI chips, TX-LWI and RX-LWI using analog PWM signaling (Fig. 7).  $P_{1o}$  and  $P_{2i}$  are the PWM output of MCV1 and the PWM input of MCV 2, respectively.

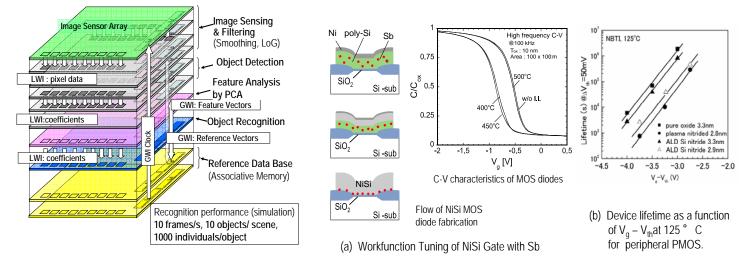

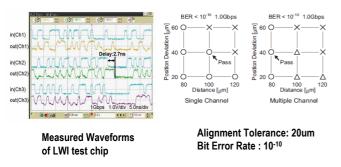

#### 4.4 Associative memory integrating learning capability

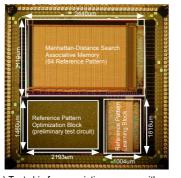

A system concept which realizes high-speed pattern matching and automatic pattern learning has been developed on the basis of an associative memory (AM) with short-term and long-term storage regions. The applied learning algorithm (Fig. 8(a)) uses a 4-step process for each learning cycle. An LSI architecture is proposed, which implements the algorithm with a fully-parallel AM, a reference-pattern-learning block and a reference-patternoptimization block. A CMOS test-chip, which verifies the architecture for an storage capacity of 64 pattern and Manhattan-distance search, has been designed. (Fig. 8(b)).

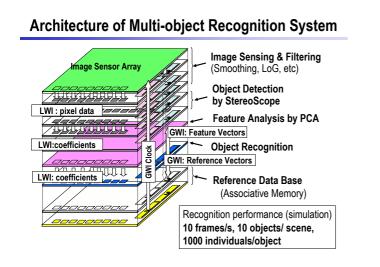

# 4.5 Architecture and Implementation of 3DCSS proto type brain system

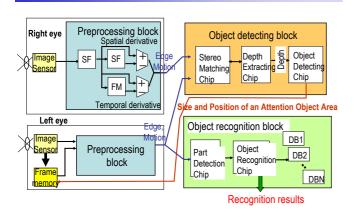

For implementing the hyper brain with real-time/ and high-level object recognition, a concept of multi-object recognition system using *3DCSS* has been studied. A higher resolution of pixels and customized functions are realized by 3DCSS. We have adopted the Principal Component Analysis and the Eigen face method for realizing multi-object detection in a natural scene and recognition under significant image variations. It is composed of wireless interconnected multi chips, early vision processor, object detector, objects recognizer and reference database composed of AM (Fig. 9). The expected performance of the system is 10 flame/s flame rate, 10 objects and 1000 data/object matching.

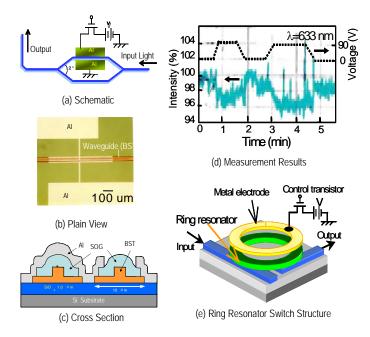

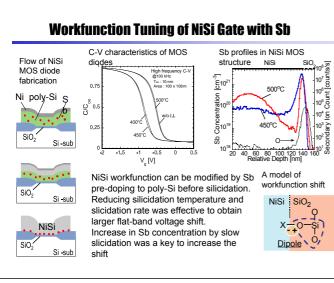

## 4.5 New MOS devices and process technologies [Work function tuning technology]

NiSi FUSI (fully silicided) gate is one of the most promising candidate for a metal gate material that replaces current dual-gate poly-Si structure to remove performance penalty due to a gate depletion effect in poly-Si gate. To realize dual metal gate structure workfunction tuning must be developed. We have evaluated NiSi workfunction shift using the Sb pre-doping. As indicated in C-V characteristics of MOS diodes, flat band voltage shift was increased by reducing silicidation temperature. Sb atoms doped to poly-Si were swept out toward remained poly-Si during silicidation. (Fig.10(a))

## [Atomic-layer deposition of gate dielectrics]

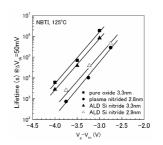

Atomic-layer-deposited (ALD) Si-nitride/SiO<sub>2</sub> stack gate dielectrics were applied to transistors for future scaled DRAMs. The stack gate dielectrics of the peripheral PMOS transistors excellently suppress boron penetration. It exhibits only slightly worse negative-bias temperature

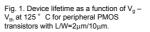

instability (NBTI) characteristics than pure gate oxide (Fig.10(b)). Enhanced reliability in NBTI was achieved compared with that of plasma-nitrided gate SiO<sub>2</sub>. NBTI of p-MOS with ultrathin SiON gate dielectric has also been investigated. The NBT-induced interface trap density ( $\Delta N_{it}$ ) under bipolar pulsed bias of frequency larger than about 10 kHz is significantly enhanced and exhibits a strong frequency dependence. The enhancement was found to be mainly governed by the fall time (t<sub>F</sub>) of the pulse waveform.

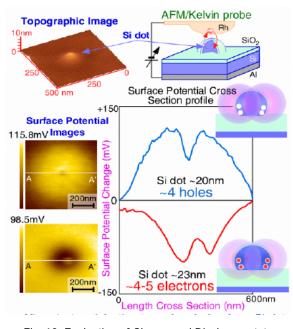

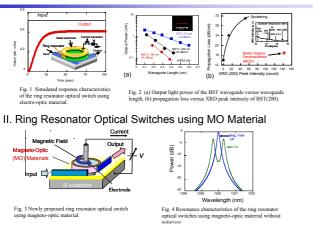

#### 4.5 Integrated Optical devices

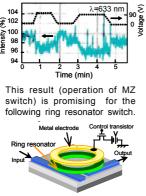

In order to overcome the speed limit of the wire interconnection, we are studying compact ring-resonator optical switches using electro-optic (EO) material, which can be monolithically integrated in LSI. We have fabricated Mach Zehnder (MZ) interferometer optical switch as shown in Fig.11, by using poly-crystal (Ba,Sr)TiO<sub>3</sub> film. And we have, for the first time, succeeded in observing the optical modulation in BST MZ modulator. The electro-optic constant calculated from the modulation efficiency is  $\gamma$ =0.45 pm/V which is about 1/100 of the single crystal LiNbO<sub>3</sub>. Although the modulation efficiency observed in this study is very small, it is meaningful that the operation of the optical modulation using monolithically integrated device is demonstrated. (Fig. 11)

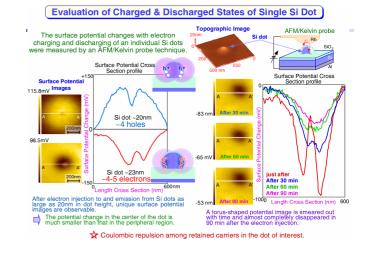

#### 4.6 Charging state of Si quantum dots

To realize multi-valued charge storage using nanometer Si dots, the precise control of electronic charged states of Si dots is one of major concerns. In that regards, we fabricated Si dots on ultra-thin oxide in a self-assembled manner by controlling the early stages of low pressure CVD. And the charge storage in nanometer Si dots has been studied. The surface potential changes were measured by an AFM/Kelvin probe technique. After electron injection and emission, unique surface potential images are observable. They indicate Coulomb repulsion among retained carriers in the dot. Such a torus-shaped potential image is smeared out with time as a result of progressive electron tunneling to the substrate, and almost completely disappeared in 90 min after the electron injection. (Fig.12)

#### 5. Conclusions

Fusing the research fields, interdisciplinary fields were formed, and innovative 3D integration technology utilizing wireless interconnections and related device and modeling techniques have been proposed. 3DCSS vision chip was designed and prototype systems are now under development.

#### Reference

[1] A. Iwata, M. Sasaki, T. Kikkawa, et. al., A 3D Integration Scheme utilizing Wireless Interconnections for Implementing Hyper Brains, ISSCC2005 Dig. of Tech. Papers, pp.262-263, 2005.

[2] M. Sasaki and A. Iwata, A 0.95mW/1.0Gbps Spiral Inductor Based Wireless Chip-Interconnection with Asynchronous Communication Scheme, Symposium on VLSI Circuits, 22-3, 2005.

Fig.7 Measurements of Multi-Chip Vision with LWI

Fig.8 Automatic Associative Memory based Reference Pattern Learning and Optimization

Fig.9 Architecture of Multi-object Recognition System

Fig. 11 Succeed in Operation of Mach Zehnder Optical Switch using (Ba,Sr)TiO<sub>3</sub> Film Monolithically Integrated on Si

Fig.10 Ultra-small MOS Device Technologies

Fig. 12 Evaluation of Charge and Discharge state of Single Si Dot

# **1Gbps Asynchronous Transmission of LWI**

Power dissipation of 1mW @ 1Gbps is obtained. Asynchronous data transfer is available.

## Automatic Associative Memory based Reference-Pattern Learning and Optimization

pattern-learning algorithm.

(b) Test chip for associative memory with high-speed matching and pattern learning.

# **Inductor Couple Transceiver for LWI**

Utilizing LC resonance, a high receive voltage is obtained with a low drive current.

20µm 20µm Transceiver

Transceiver Chip 0.18um CMOS 4 layer spiral Inductor

M.Sasaki, Presented in 2005 VLSI Sympo. on Circuits

## Measurements of Multi-Chip Vision with LWI

## Vision Chip with LWI and GWI and 3DCSS Prototype

# Process technologies for scaled MOS devices

- High-k gate dielectrics formation by Atomic Layer Deposition (ALD)

Si-nitride/SiO2 stack gate dielectrics for future scaled DRAMs.

Enhanced reliability in NBTI was achieved.

Work function tuning for NiSi Gate MOS FETs

- NiSi workfunction tuning method by Sb pre-doping to poly-Si before silicidation

- 3. Three-Dimensional MOS Devices • Beam Channel Transistor

with high current driving capability aiming at applications to power control with small chip area.

4. Functional Low-k materials for on-chip wiring.

Succeed in Operation of Mach Zehnder Optical Switch using  $(Ba,Sr)TiO_3$  Film Monolithically Integrated on Si

# Conclusions

1. Fusing the research areas, innovative ideas and technologies for tera-bit information processing have been proposed.

The key idea : Combination of Nanoelectronics and Communication

2. 3DCSS: 3D integration system utilizing Wireless interconnects was proposed, and 3DCSS vision prototype was designed toward hyper brains.

Fig. 2. Interface trap generation  $\Delta N_{it}$  as a function of  $t_{\rm R}$  (or  $t_{\rm P}$ ) under bipolar stresses at  $10^6$  Hz with a trapezoidal waveform. Inset shows a schematic waveform to define  $t_{\rm u}, t_{\rm R}, t_{\rm H}$  and  $t_{\rm E}$ . Devices have size of W/L=  $10\mu {\rm m/0.8}\mu{\rm m}$  and are stressed at  $125^\circ{\rm C}$  for  $10^3{\rm s}.$  For comparison,  ${\rm AN}_{it}$  under unipolar stress with a square waveform ( $t_{\rm T}$  =  $t_{\rm R}$ =  $t_{\rm F}$ = 4.5 ns) is also shown.

## HISIM MOS Model

| Model                                                                    | Year<br>96 98 00 02 04 |   |      |          | Nr. of<br>model<br>parameter |   | Physics based | Accuracy,<br>reliability |                                 |

|--------------------------------------------------------------------------|------------------------|---|------|----------|------------------------------|---|---------------|--------------------------|---------------------------------|

| BSIM (UC Berkeley)                                                       | Ver                    | Ш | Ver. | .IV      | _                            | 3 | 00            | ×                        | ×                               |

| Model 11 (Philips)<br>SP2000 (U. Penn. St.)<br>Surface Potential (anal.) |                        |   | -    | <u> </u> | <u> </u>                     |   |               | 0                        | ×                               |

| HiSIM (Hiroshima U.)<br>Surface Potential (exact)                        |                        |   | Ve   | er. I    | Ver. II                      | 7 | <b>5</b>      | 0                        | O Gm/Id,<br>Noise,<br>Distortio |

**Compact Model Council** will select the next MOS model by the end of 2005. **HISIM** was selected a promising candidate of 1<sup>st</sup> stage in July 2004, and is now under the testing by affiliations over the world.

By the joint research with the modeling group and the design group, HiSIM parameters of  $0.18 \mu m$  RF CMOS were extracted and simulation environment installing the latest HiSIM model was developed.

# Wireless Interconnect using Inductor Coupling

# Motivation to develop Advanced Integration

To overcome the Moore's law by utilizing 3D integration, **an inter-chip connection** is required.

Wireless inter-chip connects (reported)

|                   | •                |                     |                   |

|-------------------|------------------|---------------------|-------------------|

|                   | L,C distance     | Stacked multi-chips | Power dissipation |

| C coupling        | 1-2µm            | Not applicable      | >1mW /connect     |

| on-chip pads      | Insulator thick. | Via holes needed    |                   |

| L coupling        | 50-100μm         | Applicable          | >10mW /connect    |

| on-chip inductors | Chip thick.      | Chip-to-chip        |                   |

## **Transmission of Gaussian Monocycle Pulses**

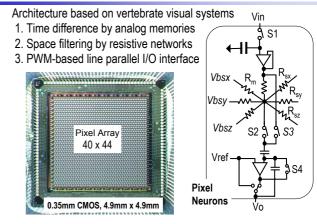

# Multi-chip Vision (MCV) and Pixel Circuit

# **Multi-object Recognition System**

#### I. Ring Resonator Optical Switches using EO Material

## **Optoelectronic Devices and Integration**

#### Integrated Optoelectronic Functional Devices

In order to overcome the speed limit of the metal interconnection in LSI, we are studying compact ring-resonator optical switches using electro-optic (EO) and magneto-optic (MO) materials, which can be monolithically integrated in LSI.

## Si-based Quantum Dots Floating gate Device

- Optical Input Switching & Memory Operation at Room Temp.

- Measurements of C-V char. of QD floating gate MOS capacitors and displacement current under light illumination and in dark.

- ·Unique hysterics due to electron charging and discharging are observed.

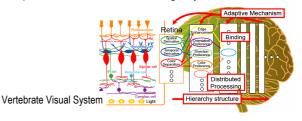

# **Motivation to implement Brain Function**

Development of architecture and algorithms to implement **brain function** utilizing advance integration technologies.

## Image Processing of Vertebrate brain:

- 1. Image feature extraction & its binding by Neural Nets

- 2. Adaptation to environment change by FB mechanism

## Vision Chip with LWI and GWI and 3DCSS Prototype