### A Brain-type Vision System using a 3-Dimensional integration with local and global wireless Interconnections

Seiji Kameda, Nobuo Sasaki, Daisuke Arizono, Masaki Odahara, Mamoru Sasaki, Takamaro Kikkawa and Atsushi Iwata Hiroshima University, 1-3-1 Kagamiyama, Higashi-Hiroshima, Hiroshima 739-8530, Japan Phone and Fax: +81-824-22-7358, E-mail: kameda@dsl.hiroshima-u.ac.jp

#### 1. Research Target

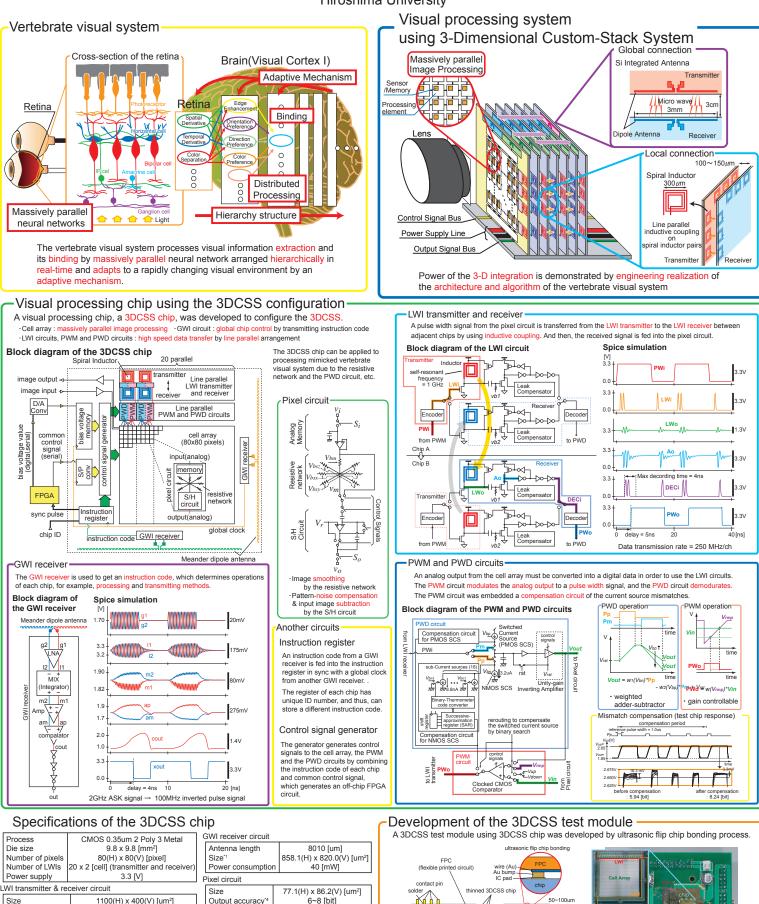

The vertebrate visual system processes huge visual information in real-time by massively parallel neural networks arranged hierarchically and adapts to a rapidly changing visual environment by an adaptive mechanism. Inspired by the unique architecture and algorithm of the vertebrate visual system, the neuromorphic vision chips or brain-type vision device, which are novel analog Very Large Scale Integrated (VLSI) circuits, have been fabricated ([1] for outlines). These neuromorphic chips, however, encounter a serious problem, namely, the trade-off between the resolution and the computational complexity of the chip. To solve the problem, multi-chip vision systems have been developed previously [2-3]. In these multi-chip systems, a high resolution and advanced functions are realized by dividing network circuits into separate chips. On the other hand, in our 21st Century COE, a visual processing system using a 3 Dimensional Custom Stack System (3DCSS) has been proposed [4]. In the system, multiple chips fabricated by various technologies and arranged hierarchically are connected by two types of wireless interconnections, which are a local wireless interconnection (LWI) [5] and a global wireless interconnection (GWI) [6]. The LWI can handle huge data, such as 2-dimensional image data, between adjacent chips due to massively parallel structure. The GWI can communicate beyond neighboring chips by microwave. Therefore, the 3DCSS is well-suited for realization of the multi-chip system mimicked the vertebrate visual system. In the present study, we developed a vision system using the 3DCSS configuration.

# 2. Visual processing chip using the 3DCSS configuration

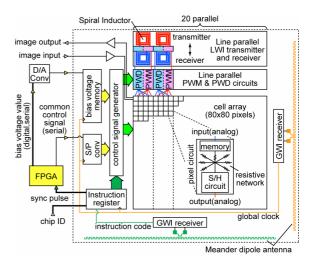

The visual processing chip was developed to configure the 3DCSS. Fig.1 shows a block diagram of the visual processing chip (3DCSS chip). The chip consists of a cell array, line parallel pulse width modulation (PWM) and demodulation (PWD) circuits, line parallel LWI transmitter and receiver, GWI receivers and a control signal generator.

In the cell array, pixel circuits are arranged in an 80 x 80 matrix. The pixel circuit consists of an analog memory, a resistive network and a sample/hold circuit (S/H). The pixel circuit is the same structure in the prototype visual processing chip [4]. An input image (analog voltage) is smoothed by the resistive network and the extent of the smoothing is controllable by external bias voltages [7]. The S/H is embedded to compensate for circuit offsets [7]. And the output voltage of the S/H varies proportionally to the time-varying input signal; therefore, the S/H can serve as a

Fig.1 Block diagram of the visual processing chip for the 3DCSS (3DCSS chip).

subtractor circuit.

Note that the analog output image from the cell array must be converted into a digital data in order to use the LWI circuits. Consequently, the PWM and PWD circuits were inserted between the cell array and the LWI circuits. The PWM and PWD circuits are arranged every 4 column of the cell array in a line  $(1 \times 20)$  to speed up the image transfer, respectively. The PWD circuit consists of switched current sources and an integration capacitor [8]. A pulse width signal from the LWI receiver fed into the switched current source is converted into current pulse and integrated on the capacitor. Accordingly, the output voltage is proportional to the input pulse width. The PWD circuit can serve as a weighted adder-subtractor by controlling the current value and direction. And the PWD circuit was embedded a compensation circuit of the current source mismatches. The PWM circuit consists of a clocked CMOS comparator [8]. The circuit generates a pulse signal until a ramp voltage is equal to the input voltage from the cell array. Thus, the output pulse width is proportional to the pixel output voltage. The ramp voltage is generated from a ramp generator incorporated in the chip. A conversion gain of the PWM is controllable by a gradient of the ramp voltage signals.

The pulse width image data is transferred from the LWI transmitter to the LWI receiver between adjacent chips by using inductive coupling [5]. The LWI transmitter and receiver were the same number as the PWM and PWD, respectively. A maximum transfer rate of the LWI circuits was 250 Mbps/cell and enough for the image data transfer. A distance between chips can be separated up to 150 um.

The LWI circuits are useful for the 2-D image data transfer due to the line parallel structure.

The GWI receiver consists of a meander type dipole antenna and a demodulation circuit. A 2.0 GHz amplitude shift keyed (ASK) signal is received by the dipole antenna and then converted into a 100 MHz pulse signal by the demodulation circuit. The GWI receiver was used to get an instruction code. The instruction code determines operations of each chip, for example, whether the LWI transmitter outputs an image data or not, and processing methods of the cell array and PWD circuit. One GWI receiver generates the instruction code and the other generates a global clock. The instruction code is fed into an instruction register in sync with the global clock. The register of each chip has unique ID number and stored a different instruction for each chip by including the ID number in the instruction code. And then, the control signal generator generates control signals to the cell array, the PWM and the PWD circuits by combining the instruction of each chip and common control signals. The GWI receiver is useful because the instruction code and the global clock must be transferred to every chip.

The 3DCSS chip can be applied to processing mimicked vertebrate visual system due to the resistive network and the PWD circuit, etc. The chip was implemented with a 0.35 um, double-poly, three metals, standard CMOS technology and the die size was  $9.8 \times 9.8 \text{ mm}^2$ . The specifications of the chip are shown in Table I.

| Process                                                                                                           | CMOS 0.35um 2 Poly 3 Metal                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die size                                                                                                          | 9.8 x 9.8 [mm <sup>2</sup> ]                                                                                                                                                        |

| Number of pixels                                                                                                  | 80(H) x 80(V) [pixel]                                                                                                                                                               |

| Number of LWIs                                                                                                    | 20 x 2 [cell] (transmitter & receiver)                                                                                                                                              |

| Power supply                                                                                                      | 3.3 [V]                                                                                                                                                                             |

| GWI receiver circuit                                                                                              |                                                                                                                                                                                     |

| Antenna length                                                                                                    | 8010 [um]                                                                                                                                                                           |

| Size <sup>*1</sup>                                                                                                | 858.1(H) x 820.0(V) [um <sup>2</sup> ]                                                                                                                                              |

| Power consumption                                                                                                 | 40 [mW]                                                                                                                                                                             |

| LWI transmitter & receive                                                                                         | r circuit                                                                                                                                                                           |

| Size                                                                                                              | 1100.0(H) x 400.0(V) [um <sup>2</sup> ]                                                                                                                                             |

| (Inductor)                                                                                                        | (300.0(H) x 300.0(V) [um <sup>2</sup> ])                                                                                                                                            |

| 31 1 8                                                                                                            | ( (TF + 1 2 2 <sup>nd</sup> + 1 2)                                                                                                                                                  |

| Number of turns                                                                                                   | 6 (Top metal: 3, $2^{m}$ metal: 3)                                                                                                                                                  |

|                                                                                                                   | 6 (Top metal: 3, 2 <sup>nd</sup> metal: 3)<br>5.6 [mW/cell] (transmitter + receiver)                                                                                                |

| Number of turns   Power Consumption*2   PWM & PWD circuit                                                         |                                                                                                                                                                                     |

| Power Consumption*2                                                                                               |                                                                                                                                                                                     |

| Power Consumption <sup>*2</sup><br>PWM & PWD circuit                                                              | 5.6 [mW/cell] (transmitter + receiver)                                                                                                                                              |

| Power Consumption*2<br>PWM & PWD circuit<br>Size<br>Resolution<br>Power                                           | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]                                                                                                    |

| Power Consumption <sup>*2</sup><br>PWM & PWD circuit<br>Size<br>Resolution                                        | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]<br>8 [bit]                                                                                         |

| Power Consumption*2<br>PWM & PWD circuit<br>Size<br>Resolution<br>Power                                           | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]<br>8 [bit]<br>(PWM) 0.66 [mW/cell]                                                                 |

| Power Consumption*2<br>PWM & PWD circuit<br>Size<br>Resolution<br>Power<br>consumption*2<br>Pixel circuit<br>Size | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]<br>8 [bit]<br>(PWM) 0.66 [mW/cell]                                                                 |

| Power Consumption*2<br>PWM & PWD circuit<br>Size<br>Resolution<br>Power<br>consumption*2<br>Pixel circuit<br>Size | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]<br>8 [bit]<br>(PWM) 0.66 [mW/cell]<br>(PWD) 1.70 [mW/cell]                                         |

| Power Consumption*2<br>PWM & PWD circuit<br>Size<br>Resolution<br>Power<br>consumption*2<br>Pixel circuit         | 5.6 [mW/cell] (transmitter + receiver)<br>332.4(H) x 344.8(V) [um <sup>2</sup> ]<br>8 [bit]<br>(PWM) 0.66 [mW/cell]<br>(PWD) 1.70 [mW/cell]<br>77.1(H) x 86.2(V) [um <sup>2</sup> ] |

Table I Specifications of the 3DCSS chip

\*1 Except antenna and wire areas.

\*2 Pulse cycle = 2.0 [us], Pulse width = 1.0 [us].

\*3 Maximum pulse width = 1.0 [us], Maximum voltage magnitude = 1.0 [V].

\*4 Depend on an input image, a smoothing area of the resistive network, and etc.

#### 3. Development of the 3DCSS test module

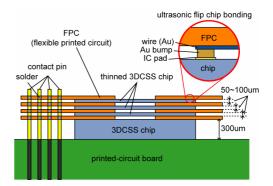

We developed a 3DCSS test module using the 3DCSS chip. Fig.2 shows a cross-section of the 3DCSS test module.

Fig.2 Cross-section of the 3DCSS test module.

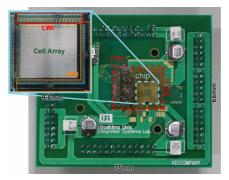

Fig.3 Photo graph of the 3DCSS test module.

We used a flexible printed circuit (FPC) to spacing between chips and wiring of power supplies, input control signals and test outputs since the FPC is very thin and stackable. The 3DCSS chips were thinned to approximate these chips except the lowest chip. The chip was bonded to the FPC by ultrasonic flip chip bonding process. These bonded FPCs were stacked on a printed-circuit board, which was a base board to make the 3DCSS user-friendly, and connected by connect pins. Fig.3 shows the photo graph of the 3DCSS test module.

#### 4. Conclusion and future

We developed the visual processing chip with LWI and GWI. And the chips were developed to the 3DCSS test module. Presently, we conduct verification experiments for the 3DCSS test module.

#### References-

- [1] A. Moini, Vision Chips (2000).

- [2] C.M. Higgins, *et al.*, Analog Integrated Circuits and Signal Processing. 24 (2000) pp.195-211.

- [3] S.-C. Liu, et al., Neural Networks. 14 (2001) pp.629-643.

- [4] S.Kameda, et al., Proc. 2nd Hiroshima Int. Workshop on Nanoelectronics for Terra-Bit Information. (2004) pp.74-75.

- [5] M. Sasaki, *et al.*, Proc. 2nd Hiroshima Int. Workshop on Nanoelectronics for Terra-Bit Information. (2004) pp.104-105.

- [6] A.B.M.H. Rashid, *et al.*, IEEE Electron Device Letters. 23(12) (2002) pp.731-733.

- [7] S. Kameda, et al., IEEE Trans. Neural Networks. 14(5) (2003) pp.1405-1412.

- [8] A. Iwata, et al., IEICE Trans. Fundamentals. E84-A(2) (2001) pp.486-496.

## A Brain-type Vision System using a 3-Dimesional integration with Local and Global Wireless Interconnections

Seiji Kameda, Nobuo Sasaki, Daisuke Arizono, Masaki Odahara, Mamoru Sasaki, Takamaro Kikkawa and Atsushi Iwata Hiroshima University

(Inductor) (300(H) x 300(V) [um<sup>2</sup>]) 6 (Top metal: 3, 2nd metal: 3) Number of turns 5.6 [mW/cell] (transmitter + receiver) Power consumption\*2 PWM & PWD circuit 332.4(H) x 344.8(V) [um2] Size Resolution 8 [bit] (PWM) 0.66 [mW/cell] Power consumption\*3 (PWD) 1.70 [mW/cell

6~8 [bit] (processing) 64.7 [uW/pixel] Power consumption (readout) 78.9 [uW/pixel] \*1 Except antenna and wire areas \*2 Pulse cycle = 2.0us, Pulse width = 1.0us \*3 Maximum pulse width = 1.0us, Maximum voltage magnitude = 1.0V. 4 Depend on an input image, a smoothing area of the resistive network, and etc

Photo graph of the 3DCSS test module

Cross section of the 3DCSS test module Presently, we conduct verification experiments for the 3DCSS test module