# Workfunction Tuning of Fully-Silicided NiSi Gate with Poly-Si Predoping

Takuji Hosoi, Kousuke Sano, Masaki Hino, Norihiro Ooishi, and Kentaro Shibahara

Research Center for Nanodevices and Systems, Hiroshima University

1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan

Phone: +81-82-424-6265, FAX: +81-82-424-3499, E-mail: hosoi@sxsys.hiroshima-u.ac.jp

#### 1. Introduction

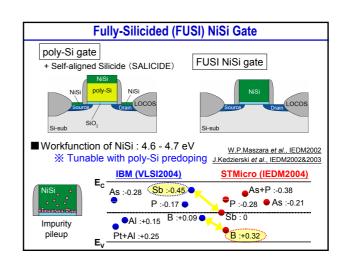

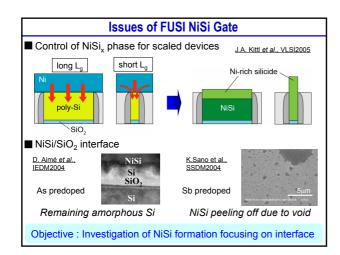

Metal gates are expected to replace conventional poly-Si gate in order to eliminate a depletion effect and boron penetration. Since single gate material with dual-workfunction is required for the existing CMOS fabrication process, workfunction tuning technique for several metals has been extensively investigated. Recently, fully-silicided (FUSI) metal gates have been demonstrated based on the extension of self-aligned silicide (SALICIDE) technology. The workfunction of FUSI NiSi gate can be tuned by impurity pileup formed at NiSi/SiO2 interface [1-5]. Furthermore, the workfunction of Ni silicide (NiSi<sub>x</sub>) depends on the composition ratio of Ni/Si [6]. However, the workfunction tunable range of FUSI NiSix is still insufficient for high performance CMOS devices. Furthermore, Ni silicide phase difference between longand short-channel FETs should be addressed [7]. Issues such as voiding [4, 8] and a-Si formation [9] were also found in FUSI gate structure. Therefore, it is important to establish the FUSI process taking into account the controllability of silicide formation. In this paper, not only the workfunction shift in FUSI NiSi gate with poly-Si predoping but also side effects such as the void formation at NiSi/SiO<sub>2</sub> interface and controllability of silicide phase formation are discussed.

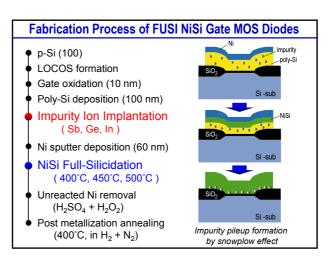

# 2. Experiment

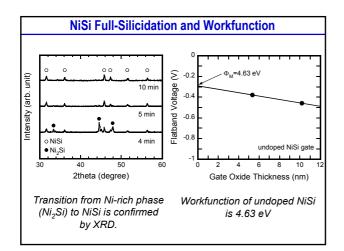

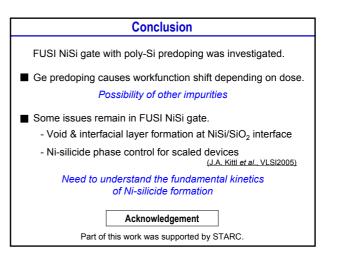

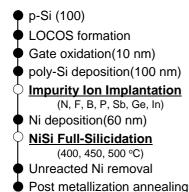

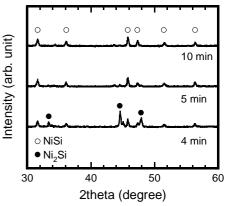

Figure 1 shows the FUSI NiSi gate MOS diode fabrication process flow. The poly-Si predoping conditions (implantation species, dose, and energy) are listed in Table I. Silicidation was carried out at 400 °C, 450 °C, or 500 °C by in-situ lamp heating in a vacuum just after Ni deposition. Although Ni-rich phase (Ni<sub>2</sub>Si) is found at the initial stage of silicidation, transformation to Ni monosilicide phase (NiSi) is completed after prolonged anneals, as shown in Fig. 2. NiSi gate workfunction is extracted from C-V characteristics of MOS diodes with area of 10<sup>-4</sup> cm<sup>2</sup>. As shown in Fig.3, the workfunction of undoped NiSi gate is determined to be 4.63 eV.

### 3. Results and Discussion

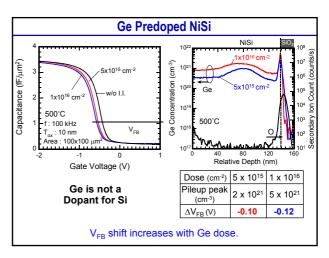

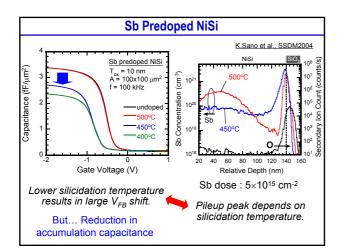

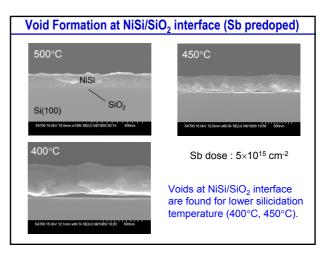

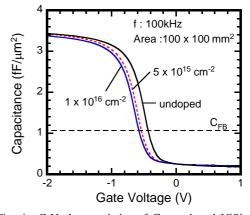

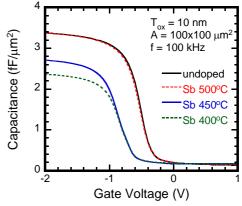

Table I shows a summary of flatband voltage ( $V_{FB}$ ) shift for various impurity species [10]. It is noteworthy that Ge, which is not a dopant for Si, caused the  $V_{FB}$  shift. Figure 4 shows the C-V characteristics of Ge predoped NiSi gate MOS diodes with two different implantation doses. The  $V_{FB}$  shift increases with implantation dose. The Ge depth profile in NiSi MOS structure measured by back-side SIMS confirms that Ge concentration at the oxide interface and in NiSi film is dependent on the implantation dose. In the case of Sb predoped NiSi MOS diodes, silicidation at the 500 °C resulted in a small  $V_{FB}$  shift, but the larger  $V_{FB}$  shift (-0.34 eV) was obtained for lower silicidation temperature (Fig. 5). This difference also originates from the Sb concentration at NiSi/SiO<sub>2</sub> interface. On the other hand, it should be noted that reduction in the

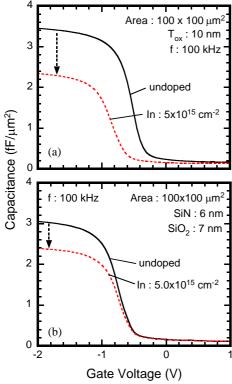

accumulation capacitance was observed for 400  $^{\circ}$ C and 450  $^{\circ}$ C. In addition, partial NiSi film peeling was found after unreacted Ni removal with acid only for silicidation temperature below 450  $^{\circ}$ C [8]. This is attributed to void formation at the NiSi/SiO<sub>2</sub> interface.

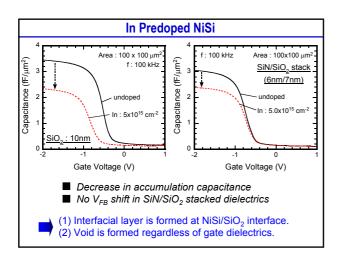

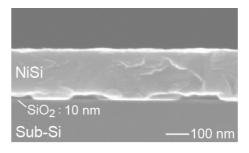

The similar side effect was also observed for In predoped sample. As shown in Fig. 6(a), reduction in accumulation capacitance in C-V characteristics and the V<sub>FB</sub> shift were observed. We speculated that In driven to the oxide interface formed a interfacial layer by the reaction with the oxide, which leads to charge formation and increase in insulator thickness. To judge accuracy of this speculation, SiN was deposited on the oxide film to prevent the interfacial reaction. As a result, though V<sub>FB</sub> shift decreased, accumulation capacitance reduction still remained as shown in Fig. 6(b). Cross-sectional observation by SEM in Fig. 7 revealed that the capacitance reduction is attributed to void formation at the interface. Although the void formation mechanism is not clear yet, it is assured that impurity concentration in the vicinity of the interface is the key factor. This voiding should be noted as a potential roadblock against practical use of fully silicided NiSi gate.

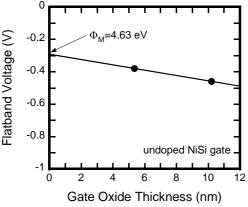

# 5. Conclusion

Full silicidation of NiSi gate with poly-Si predoping for workfunction tuning was investigated. It was found that Ge that is not a dopant for Si causes the workfunction shift depending on the doping concentration. On the other hand, there still exist some problems such as the void formation and the interfacial reaction at the NiSi/SiO<sub>2</sub> interface. Previous works on FUSI NiSi gate have been mainly focused on workfunction tuning [1, 3], but recently Kittl *et al.* have addressed Ni silicide phase control in FUSI process in terms of the device scalability [7]. Thus, a fundamental understanding of the kinetics of silicide formation is essential for practical application,

#### Acknowledgements

Part of this work was supported by the Semiconductor Technology Academic Research Center (STARC).

# References

- [1] J. Kedzierski et al., IEDM Tech. Dig. 2002, p. 247.

- [2] J. Kedzierski et al., IEDM Tech. Dig. 2003, p. 315.

- [3] W. P. Maszara et al., IEDM Tech. Dig. 2002, p. 367.

- [4] C. Cabral, Jr. et al., Proc. on VLSI Tech. Symp. 2004, p. 184.

- [5] K. Sano et al., Ext. Abstr. SSDM 2004, p. 456.

- [6] K. Hosaka et al., Proc. on VLSI Tech. Symp. 2005, p. 66.

- [7] J. A. Kittl et al., Proc. on VLSI Tech. Symp. 2005, p. 72.

- [8] K. Sano et al., Jpn. J. Appl. Phys. 44, p. 3774 (2005).

- [9] D. Aimé et al., IEDM Tech. Dig. 2004, p. 87.

- [10] T. Hosoi et al., Proc. of 3rd Hiroshima Int. Workshop on Nanoelectronics for Terra-Bit Information Processing, 2004, p. 70.

Fig. 1 Fabrication process flow of fully silicided NiSi gate MOS diodes.

Table I Impurity implantation conditions and resulting  $V_{FB}$  shift. Standard silicidation temperature was 500 °C.

|    | Dose(cm <sup>-2</sup> ) | Energy(KeV) | ΔV <sub>FB</sub> (V) |

|----|-------------------------|-------------|----------------------|

| N  | 5.0 x 10 <sup>15</sup>  | 10          | ~ 0                  |

| F  | 2.5 x 10 <sup>15</sup>  | 10          | ~ 0                  |

| В  | 1.0 x 10 <sup>15</sup>  | 5           | > 0                  |

| Р  | 5.0 x 10 <sup>15</sup>  | 15          | < 0                  |

| Sb | 5.0 x 10 <sup>15</sup>  | 30          | < 0                  |

| Ge | 5.0 x 10 <sup>15</sup>  | 30          | < 0                  |

| ln | 5.0 x 10 <sup>15</sup>  | 30          | < 0 ?                |

Fig. 2 XRD spectra of NiSi MOS structure with various silicidation time at 500 °C.

Fig. 3 Flatband voltage of undoped FUSI NiSi gate MOS iodes extracted from the C-V characteristics as a function of gate oxide thickness.

Fig. 4 C-V characteristics of Ge predoped NiSi gate MOS diodes.

Fig. 6 C-V characteristics of Sb predoped NiSi gate diodes. Gate insulators are  $SiO_2$  (a) and  $SiN/SiO_2$  stack (b)

Fig. 5  $\,$  C-V characteristics of Sb predoped NiSi gate MOS diodes.

Fig. 7 Cross sectional SEM micrograph of In predoped NiSi/SiO2/Si interface. Voids at the NiSi/SiO2 interface were found.

P-26

# Workfunction Tuning of Fully-Silicided NiSi Gate with Poly-Si Predoping

T. Hosoi, K. Sano, M. Hino, N. Ooishi, and K. Shibahara

Research Center for Nanodevices and Systems, Hiroshima University

1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, JAPAN

Phone: +81-82-424-6265 Fax: +81-82-424-3499

E-mail: hosoi@sxsys.hiroshima-u.ac.jp

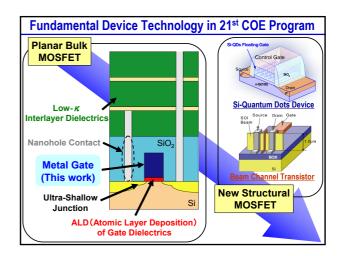

# Why Metal Gate?

#### ■ Merit & Task of Metal Gate

Merit: © Elimination of poly-Si depletion effect

→ Thinning of EOT

$I_{\rm D} = \frac{1}{2} \frac{W}{L} \mu C_{\rm ox} (V_{\rm g} - V_{\rm th})^2$

No boron penetration

Mobility enhancement (S. Datta et al., IEDM2003)

Task : ▼ CMOS process compatibility

▼ Dual workfunction for p-/n-MOSFET (pFET: 5.17eV, nFET: 4.05 eV)

■ Metal Candidate

TiN, TaN, FUSI, W, · · · etc

Fully-Silicided gate (NiSi, PtSi,...)