# **Characterization of Newly Developed 3-D Parallel-Triple Gate MOS Transistor**

Kiyoshi Okuyama, Koji Yoshikawa, and Hideo Sunami

Research Center for Nanodevice and Systems, Hiroshima University

Phone: +81-824-24-6265, Fax: +81-824-22-3499,

E-mail: okuyama@sxsys.hiroshima-u-ac.jp

## 1. Introduction

It is known that double gate structure has advantage to control the short channel effect as compared with conventional bulk devices. Three-dimensional (3-D) device structure such as FinFET that realize double gate structure vertically have been developed [1]. On the other hand, for 3-D devices with vertical channel, drive current per unit planer area can be increased with the increase in the beam height. In this viewpoint, 3-D transistor with higher aspect ratio such as beam channel transistor (BCT) [2] and corrugated channel transistor (CCT) [3] have been proposed and successfully fabricated. Thus, there are some possibilities to utilize advantage of 3-D structure. Then, the progress of new structure and/or new operation is important. In this report, a new vertical structure transistor is proposed.

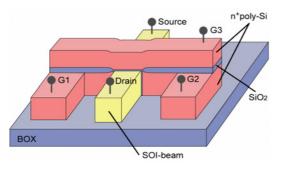

The structure of proposed device is shown in Fig. 1. In this structure, three transistors that are formed on a SOI beam can operate independently. This can apply to parallel part of a logic circuit, for example a part of NAND gate. Since transistors are integrated vertically, this structure has an advantage from the viewpoint of area efficiency.

Fig. 1 A proposed device that has three independent gate electrodes.

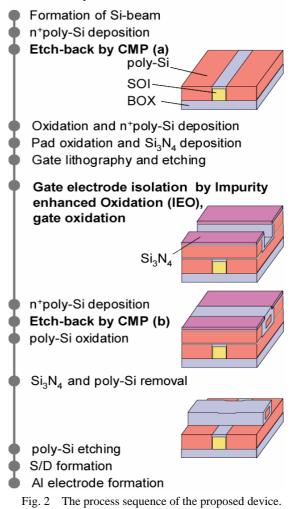

In the fabrication of this device, it is important to form three gate electrodes using self-aligned process to realize tight compaction. The fabrication process is devised in consideration of this point. The process sequence is shown in Fig. 2. Formation of isolation layer for gate electrodes, and leveling of poly-Si are key techniques to realize the proposed device.

### 2. Device fabrication

Boron-doped SOI wafers of 10  $\Omega$ -cm in resistivity are used as starting material. After formation of SOI beams with 250 nm in height by reactive ion etching (RIE) and gate oxide film on the sidewall by thermal oxidation, poly-Si is deposited by thermal chemical vapor deposition and doped with phosphorous by POCl<sub>3</sub> gasses. The resistivity of the n<sup>+</sup>poly-Si film is almost  $5x10^{-4} \Omega$ -cm. Subsequent leveling of n<sup>+</sup>poly-Si is

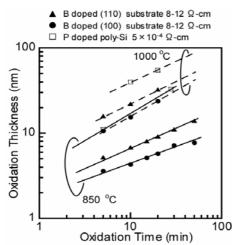

achieved by chemical mechanical polishing (CMP). Multi-layer films consist of thermal oxide, n<sup>+</sup>poly-Si, and  $Si_3N_4$  are deposited on the planarized surface for the top gate electrode formation. After patterning of gate electrodes and etching processes, formation of isolation layer that separates poly-Si wirings is needed. Since gate oxide film of the top gate and the isolation layer of gate electrodes are formed simultaneously, it is important to enlarge the ratio of oxide thickness of Si substrate and poly-Si. From this reason, the impurity enhanced oxidation (IEO[4]) is introduced. Oxide thicknesses of phosphorous doped n<sup>+</sup>poly-Si and boron doped Si are shown in Fig. 3. The ratio of oxide thickness exceeds almost 4.4 times at 850 °C while it is about 2.7 times at 1000 °C. The former condition is adopted in this fabrication process. After the IEO, n<sup>+</sup>poly-Si deposition, and its leveling by CMP etch-back, top gate electrodes are covered with its own oxide by thermal oxidation. Side-gate electrodes are formed by RIE utilized the top gate as an etching mask.

#### **Process sequence**

Fig. 3 Impurity enhanced oxidation at 850  $^{o}C$  and 1000  $^{o}C$   $\,$  (  $O_{2}$  = 2 slm ).

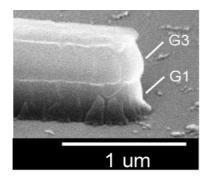

Fig. 4 An SEM image of two layer  $n^+$  poly-Si wiring with 300-nm width.

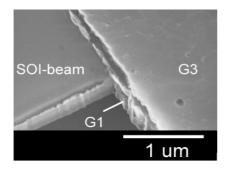

Fig. 5 A bird's eye view of the fabricated device. Side-gate electrode (G1) and top one (G3) are formed successfully on an SOI beam.

The proposed triple gate structure was successfully fabricated as shown in Figs. 4 and 5. Subsequent source and drain formation is achieved by arsenic ion implantation and rapid thermal annealing.

## 3. Characterization and Discussion

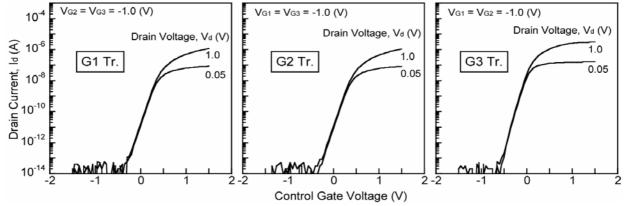

$I_d$ - $V_g$  characteristics of fabricated 3-D parallel-triple gate transistor are shown in Fig. 6. While no channel implantation causes weak cut-off, gate voltage of other gates are fixed -1.0 V in the measurement. Thus, normal operation of each transistor is confirmed. The drain current of top gate (G3) is 2.8 times at  $V_d = 1.0$  V than that of side gate (G1 and G2) since the aspect ratio of devise is about 0.5. Measurements on various beam width are in progress.

### 4. Summary

A novel 3-D Transistor structure is proposed and successfully fabricated utilizing the IEO and CMP etch-back. Normal operation of each transistor is confirmed. Characterization on several conditions is in progress.

#### 5. References

- [1] Y-K. Cho, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Andersen, T-J. King, J. Bokor, and C. Hu, IEDM Tech. Dig., pp. 421-424, 2001.

- [2] A. Katakami, K. Kobayashi, and H. Sunami, Jpn. J. Appl. Phys., Vol. 43, No. 4B, pp. 2145-2150, 2004.

- [3] T. Furukawa, H. Yamashita, and H. Sunami, Jpn. J. Appl. Phys., Vol. 42, Part 1, No. 4B, pp. 2100-2105, 2003.

- [4] H. Sunami, J. Electrochem. Soc., 125, pp. 892-897, 1978.

Fig. 6  $I_{d}$ - $V_{g}$  characteristics for parallel-triple gate transistor with 250 nm in height and 540 nm in width SOI beam and 4-um gate length.

#### Characterization of Newly Developed Introduction 3-D Parallel-Triple Gate MOS Transistor It is known that double gate structure has an advantage to control the short channel effect as compared with conventional bulk devices. 3-D devices such as FinFET [1] and tri-gate transistor [2] with multi-gate structure have been proposed and developed as candidates for further scaled MOS devices in future Kiyoshi Okuyama, Koji Yoshikawa, and Hideo Sunami Besides the scaling, some area-conscious Research Center for Nanodevice and Systems, Hiroshima University applications resulting in large drivability within small planer area have been proposed [3, 4]. Phone: +81-82-424-6265, Fax: +81-82-424-3499, 1 μm E-mail: okuyama@sxsys.hiroshima-u-ac.jp Beam channel transistor [3] Corrugate channel transistor [4] 4th COE workshop Sept. 16, 2005 Objectives : Development of transistor structure and its formation process for Hiroshima University appropriate application of 3-D transistor In this report, a new 3-D MOSFET with novel fabrication process is proposed Fabrication process Proposed device rocess sequence Formation of Si-beam by RIE Parallel-Triple Gate MOS Transistor n<sup>+</sup>poly-Si deposition poly-Si Etch-back by CMP (a) Operation Modes SOI Formation of G1 and G2 BOX • G3 using a G3 pattern Oxidation and n<sup>+</sup>poly-Si deposition 엓 Pad oxidation and Si3N4 deposition (a) Single-gate (b) Doubl Gate lithography and etching by RIE Formation of isolation layer by Impurity enhanced oxidation (IEO [5]) Si<sub>3</sub>N<sub>4</sub> Hard mask (G3) For parallel-connected three transistor operation, This device has an advantage from the viewpoint Gate oxidation of area efficiency n<sup>+</sup>poly-Si deposition E · futuro oiz Etch-back by CMP (b) Poly-Si oxidation Three gate electrodes formed 105F<sup>2</sup> 42F<sup>2</sup> Anisotropic dry etching on an SOI beam Independently G1 G3 G2 " (X) (X) (X) Si3N4 and poly-Si removal Side-gate formation by RIE .... S/D formation by ion implantation Usual parallel connection of triple transistors. The proposed device Al electrode formation Experimental Gate electrode isolation by the impurity enhanced oxidation [5] Leveling by CMP etch back Thick isolation layer CMP (a) Poly-S CMP (b) Enhancement of the ratio of , Stopper (Si3N4) Oxide thickness of SOI and ner (SiO2) IEO Poly poly-Si is needed. I BOX SOI Thin gate oxide BOX 100 Ratio of oxide thickness 1000 °C 21 تا يتيين p(100) substrate : P doped poly-Si (mu 850 °C 1:4.4 The ratio exceeds almost 1000 °C 1:2.7 4.4 at 850 °C Oxide SiM 00 nr Resisitivity A good configuration is obtained. A layout patterns with dummy Poly-Si Areas of SOI-beams P doped n+poly-Si : 5x10-4 (Ω-cm) $O_2 = 2 \, \text{slm}$ in this proces B doped p(100) and p(100) sub. : 8-12 (Ω-cm) SiO, Dummy patterns are introduced to prevent dishing and erosion. 10 Oxidation Time (min) IEO at 850 °C (O2 = 2 slm, 14 min) Result Summary Obtained gate structures A novel 3-D transistor structure and its fabrication process are proposed. In this process, G1 and G2 are delineated using a G3 pattern as an etching 0.3 um L/S l um L/S mask The impurity enhanced oxidation and CMP etch back are introduced in this fabrication. The impurity enhanced oxidation : The oxide thickness ratio exceeds almost 4.4 at 850 °C 1 um

$I_D - V_D$  characteristics

Side-gate, G1 Tr.

10

(¥) 10

Drain Current, 10

10

nm \Ale = 250 nm | a

Vo (V) 1.0

0.05

= 255 nm Ws = 250 nm | c = 680 n

te, G3 Tr.

\$ \$ \$ \$

te Voltage, VG (V)

Vo (V) 1.0

0.05

80 (S

g

60

40 P

20 20

Normal operations on

each gate are confirmed.

The gate voltage of other two gates is fixed at -1.0 V

Gate oxide thicknesses G1 and G2 : 4.8 nm G3 : 4.7nm (No channel implantation)

single-gate mode for

CMP etch back : Dummy patterns are introduced to prevent dishing and erosion

The proposed device is successfully fabricated on novel self-aligning techniques using these processes and normal operations on single-gate mode for each gate are confirmed.

#### References

K.C. Cho, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Andersen, T.-J. King, J. Bokor, and C. Hu, IEDM Tech. Dig., pp. 421-424. 2001.

[2] B. Doyle, B. Boynoro, S. Datta, M. Doczy, S. Harenand, B. Jin, J. Kavaliere, T. Linton, R.Rios, and R. Chau. Symposium on VLSI Technology Digest of Technical Paper, (2003).

[3] A. Katakami, K. Kobayashi, and H. Sumami, Jon. J. Appl. Phys., Vol. 42, pp. 416, 2016.

[4] T. Furukawa, H. Yamashita, and H. Sumami, Jun. J. Appl. Phys., Vol. 42, pp. 4176, 2165, 2003.

[5] H. Sunami, J. Electrochem. Soc., 125, pp. 892-897, 1978.