## Development of Reliable High-k Gate Dielectrics for Scaled MOSFETs

Anri Nakajima

Reserach Center for Nanodevices and systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan Phone:81-82-424-6274, Fax:81-82-424-3499:nakajima@sxsys.hiroshima-u.ac.jp

### 1. Introduction

In this COE project, the subject of our group is the research and development of future reliable gate dielectrics. The subject includes atomic-layerdeposition (ALD) of silicon nitride, ALD high–kgate dielectrics, and plasma nitrided SiON gate dielectrics, etc. Here, static and dynamic bias temperature instability in p- and n-MOSFETs having plasma nitrided SiON gate dielectrics was investigated in detail. ALD Si nitride/SiO<sub>2</sub> gate dielectrics were applied to future scaled DRAM. ALD growth of HfO<sub>2</sub> was also investigated by the alternate exposure of tetrakis diethylmethylamino hafnium and water on both Si and Ge substrates.

# 2. Static bias temperature instability (BTI )characteristics

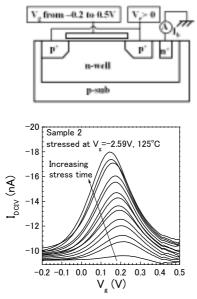

instability (BTI) Bias temperature in MOSFETs has emerged as one of the most critical reliability issues with scaling down of gatedielectric thickness. Based on the reactiondiffusion (R-D) model, the degradation of device performance is widely accepted to be caused by interface trap generation  $(\Delta N_{it})$  and oxide charge buildup ( $\Delta N_{ot}$ ). To reveal the detail mechanism of BTI, N<sub>it</sub> and N<sub>ot</sub> should be measured accurately and separately. For this purpose, we proposed a modified direct-current current-voltage (DCIV) method [1]. By subtracting the DCIV current measured at  $V_s = V_d = 0$  from that measured at  $V_s = V_d = V_e(\neq 0)$  with carefully selecting a suitable V<sub>e</sub> value, the direct-tunneling-current effect of the ultrathin gate dielectrics can be minimized, leading to a clear DCIV peak. Figure 1 shows the configuration for DCIV measurement and the typical modified DCIV curves. Here, N<sub>it</sub> can be calculated from the DCIV peak height while  $\Delta N_{ot}$ is closely related to the peak position shift. Moreover, DCIV curves recorded at different temperatures were found to give a similar N<sub>it</sub> value, leading to the simplification of the procedure for temperature dependence studies.

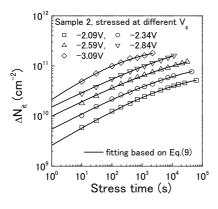

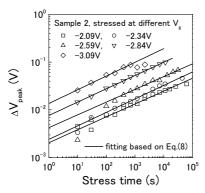

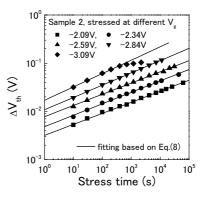

The above modified DCIV method (Figs. 2 and 3) and a conventional subthreshold characteristic measurement (Fig. 4) were applied to study negative BTI of pMOSFETs with ultrathin plasma-nitrided SiON gate dielectrics [2]. The nitrogen peak is around the middle of the base SiO<sub>2</sub> (2 nm) and the concentrations are 9%, 12% and 15% for samples 1, 2, and 3, respectively. We found that during the NBT stress,  $\Delta N_{ot}$  is not linearly related to  $\Delta N_{it}$  (Figs. 2 and 3). At the earlier stress times,  $\Delta N_{it}$  dominates the threshold voltage shift ( $\Delta V_{th}$ ) and  $\Delta N_{ot}$  is negligible. At the longer stress times,  $\Delta N_{it}$  deviates from the powerlaw time dependence, showing a saturation effect (Fig. 2). On the other hand,  $\Delta N_{ot}$  still has a powerlaw dependence on stress time so that the contribution of  $\Delta N_{ot}$  to  $\Delta V_{th}$  increases (Fig. 3). Increasing the nitrogen concentration of the plasma-nitrided SiON gate dielectric from 9 to 15% did not detectably enhance the NBTI while the suppression of boron penetration and the EOT reduction have been significantly improved. It indicates that plasma-nitrided SiON is a superior gate dielectric from the viewpoint of NBTI.

### **3.** BTI characteristics under highfrequency bipolar gate bias

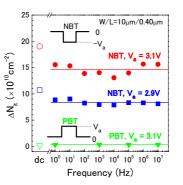

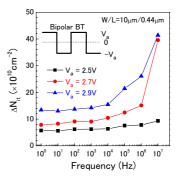

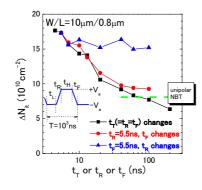

NBTI of p-MOSFETs with ultrathin SiON gate dielectric has been investigated under various gate bias configurations [3-6]. The NBT-induced  $\Delta N_{it}$ under unipolar bias is essentially lower than that under static bias, and is almost independent of the stress frequency up to 10 MHz (Fig. 5). On the contrary,  $\Delta N_{it}$  under bipolar pulsed bias of frequency larger than about 10 kHz is significantly enhanced and exhibits a strong frequency dependence (Fig. 6). The enhancement was found to be mainly governed by the fall time  $(t_F)$  of the pulse waveform (Fig. 7), namely, the transition time of the silicon surface potential from strong accumulation to strong inversion, rather than the pulse rise time  $(t_R)$  and the pulse duty factor (D). The enhancement decreases significantly with  $t_F$ increasing, and is almost eliminated when t<sub>F</sub> is larger than ~ 60 ns. The degradation enhancement is attributed to the transient electrons trapped in the interface states upon switching of the silicon surface potential from accumulation to inversion.

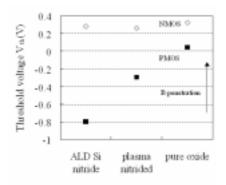

## 4. Application of ALD Si niutride/SiO<sub>2</sub> gate dielectrics to future DRAMs

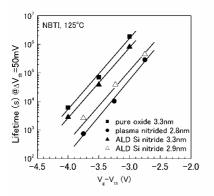

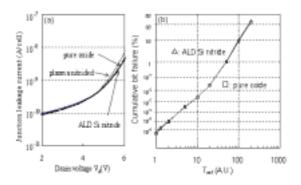

ALD of Si nitride is one of the key technologies for the next generation gate dielectrics [7,8]. ALD Si-nitride/SiO<sub>2</sub> stack gate dielectrics were applied to high-performance transistors for future scaled DRAMs [9]. The stack gate dielectrics of the peripheral PMOS transistors excellently suppress boron penetration (Fig. 8). ALD stack gate dielectrics exhibit only slightly worse negative-bias temperature instability (NBTI) characteristics than pure gate oxide (Fig. 9). Enhanced reliability in NBTI was achieved compared with that of plasma-nitrided gate SiO<sub>2</sub> (Fig. 9). Memory-cell (MC) NMOS transistors with ALD stack gate dielectrics show slightly smaller junction leakage than those with plasmanitrided gate SiO<sub>2</sub> in a high-drain-voltage region, and have identical junction leakage characteristics to transistors with pure gate oxide (Fig. 10). MCs having transistors with ALD stack gate dielectrics and those with pure gate oxide have the identical retention-time distribution (Fig. 10). Taking the identical hole mobility for the transistors with ALD stack gate dielectrics to that for the transistors with pure gate oxide both before and after hot carrier injection [8] into account, the ALD stack dielectrics are a promising candidate for the gate dielectrics of future high-speed, reliable DRAMs.

## 5. Atomic-Layer-Deposition of HfO<sub>2</sub> on Si and Ge Substrates

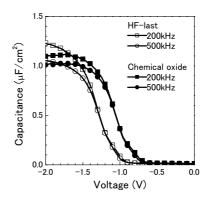

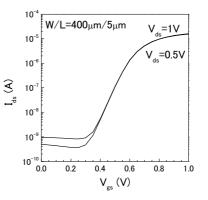

We have developed ALD growth of ZrO<sub>2</sub> on Si substrate using zirconium tertiary-butoxide and water [10,11]. This time, ALD growth of HfO<sub>2</sub> was investigated on both Si and Ge substrates by alternate of the exposure tetrakis diethylmethylamino hafnium (termed as TDEAH) and water [12]. Capacitance-voltage (C-V) characteristics on the bare Si and on the chemically oxidized Si show no hysteresis and kvalue of 12-14 (Fig. 11). MOSFETs with the ALD HfO<sub>2</sub> gate dielectrics on Si substrate were demonstrated using a simple one-mask fabrication process (Fig. 12). Stoichiometric HfO<sub>2</sub> can be deposited on Ge, whereas further studies are necessary to improve the quality.

#### 6. Conclusion

For the development of future reliable gate dielectrics, reliability of plasma nitrided SiON gate dielectics was studied in detail by the measurements of static and dynamic bias temperature instability. Applicability of ALD Sinitride/SiO<sub>2</sub> stack gate dielectrics to future scaled DRAMs was also investigated. Moreover, ALD

growth of  $HfO_2$  was investigated on both Si and Ge substrates with TDEAH and water.

#### Acknowledgement

The author wishes to thank Prof. S. Yokoyama, Dr. S. Zhu, Dr. Q.D.M. Khosru, Y. Yokoyama, H. Ishii, T. Kasai, T. Kidera, T. Yoshimoto, T. Ohashi, and Dr. H. Miyake for their cooperation.

#### References

- [1] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Modified Direct-Current Current-Voltage Method for Interface Trap Density Extraction in Metal-Oxide-Semiconductor Field-Effect-Transistor with Tunneling Gate Dielectrics at High Temperature," Jpn. J. Appl. Phys. Vol. 44, No. 2A, pp. L60–L62, Jan. (2005).

- [2] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Interface trap and oxide charge generation under negative bias temperature instability of p-channel metaloxide-semiconductor field-effect transistors with ultrathin plasma-nitrided SiON gate dielectric," J. Appl. Phys. Vol. 98, No. 11, Art. No. 114504 (6 pages) Dec. (2005).

- [3] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Interface Trap Generation Induced by Charge Pumping Current under Dynamic Oxide Field Stresses," IEEE Electron Device. Lett. Vol. 26, No.3, pp. 216-218, March (2005).

- [4] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Enhancement of BTI Degradation in pMOSFETs under High-Frequency Bipolar Gate Bias," IEEE Electron Device. Lett. Vol. 26, No. 6, pp. 387-389, June (2005).

- [5] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Pulse Waveform Dependence on Ac Bias Temperature Instability in pMOSFETs," IEEE Electron Device. Lett. Vol. 26, No. 9, pp. 658-660, Sept. (2005).

- [6] Shiyang Zhu, Anri Nakajima, Takuo Ohashi, and Hideharu Miyake, "Pulse Waveform Dependence on AC Bias Temperature Instability in pMOSFETs," IEEE Electron Device Lett. Vol. 26, No. 9, pp. 658-660, Sept. (2005).

- [7] Anri Nakajima, Hiroyuki Ishii, Tetsuya Kitade, and Shin Yokoyama, "Atomic-Layer-Deposited Ultrathin Si-Nitride Gate Dielectrics ---A Better Choice for Sub-tunneling Gate Dielectrics---," Technical Digest of the 2003 IEEE International Electron Devices Meeting (Washington, D.C., Dec. 8-10, 2003) pp.657-660.

- [8] Anri Nakajima, Quazi D. M. Khosru, Tetsurou Kasai, and Shin Yokoyama, "Carrier Mobility in p-MOSFET with Atomic-Layer-Deposited Si-Nitride/SiO<sub>2</sub> Stack Gate Dielectrics," IEEE Electron Device Lett. Vol. 24, No. 7, pp. 472-474, July (2003).

- [9] Anri Nakajima, Takuo Ohashi, Shiyang Zhu, Shigeyuki Yokoyama, Shigetomi Michimata, and Hideharu Miyake, "Atomic-Layer-Deposited Si-Nitride/SiO<sub>2</sub> Stack Gate Dielectrics for Future High-Speed DRAM with Enhanced Reliability," IEEE Electron Device. Lett. Vol. 26, No. 8, pp. 538-540, August (2005).

- [10] Anri Nakajima, Toshirou Kidera, Hiroyuki Ishii, and Shin Yokoyama, "Atomic-layer deposition of ZrO<sub>2</sub> with a Si nitiride barrier layer," Appl. Phys. Lett. Vol. 81, No. 15, pp. 2824-2826, Oct. (2002).

- [11] Hiroyuki Ishii, Anri Nakajima, and Shin Yokoyama, "Growth and electrical properties of atomic-layer deposited ZrO<sub>2</sub>/Si-nitride stack gate dielectrics," J. Appl. Phys. Vol. 95, No. 2, pp.536-542, Jan. (2004).

- [12] Yuichi Yokoyama, Shiyang Zhu, and Anri Nakajima, "Atomic Layer Deposition of  $HfO_2$  using  $Hf[N(C_2H_5)_2]_4$  and  $H_2O$ ," Jpn. J. Appl. Phys. Vol. 45, No. 9A, Sept. (2006) pp. 7091-7093.

Figure 1 (top) Bias configuration of DCIV measurement. (bottom) Typical modified DCIV curves of a pMOSFET with ultrathin SiON gate dielectric before and after stress.

Figure 2 Stress time evolution of interface trap generation ( $\Delta N_{it}$ ) for sample 2 stressed at 125°C at different voltages. Fitting lines are also shown.

Figure 3 Stress time evolution of DCIV peak position shift ( $\Delta V_{peak}$ ) for sample 2 stressed at 125°C at different voltages and linear fitting.

Figure 4 Stress time evolution of threshold voltage shift ( $\Delta V_{th}$ ) for sample 2 stressed at 125°C at different voltages, and linear fitting based on assumption of the power-law dependence.

Figure 5 Interface trap generation  $\Delta N_{it}$  as a function of stress frequency at different stress voltage  $V_{stress}$ , under unipolar pulsed stress (L=0.40 $\mu m$ ) for a pMOSFET with plasma-nitrided SiO<sub>2</sub> gate dielectrics. Stressed at 125°C for 10<sup>3</sup>s. The data of dc stresses are also shown for comparison, whose nominal stress time is 500s. Inset is a schematic waveform applied on the gate.

Figure 6 Interface trap generation  $\Delta N_{it}$  as a function of stress frequency at different stress voltage  $V_{stress}$ , under bipolar pulsed stress (L=0.44 $\mu$ m) for a pMOSFET with plasma-nitrided SiO<sub>2</sub> gate dielectrics. Stressed at 125°C for 10<sup>3</sup>s.

Figure 7 Interface trap generation  $\Delta N_{it}$  as a function of  $t_R$  (or  $t_F$ ) under bipolar stresses at 10<sup>6</sup> Hz with a trapezoidal waveform. Inset shows a schematic waveform to define  $t_L$ ,  $t_R$ ,  $t_H$  and  $t_F$  for a pMOSFET with plasma-nitrided SiO<sub>2</sub>. Devices have size of W/L=10µm/0.8µm and are stressed at 125°C for 10<sup>3</sup>s. For comparison,  $\Delta N_{it}$  under unipolar stress with a square waveform ( $t_T = t_R = t_F = 4.5$  ns) is also shown.

Figure 8  $V_{th}$  of peripheral NMOS and PMOS transistors. L/W=1 $\mu$ m/10 $\mu$ m.

Figure 9 Device lifetime as a function of  $V_g - V_{th}$  at 125 °C for peripheral PMOS transistors with  $L/W=2\mu m/10\mu m$ .

Figure 10 Memory-cell characteristics. (a) Junction leakage current of the transistors with the three kinds of gate dielectrics. (b)Data-retention characteristics of samples with the transistors having ALD stack gate dielectrics and pure gate oxide.

Figure 11 Capacitance-voltage curves measured at 200 and 500 kHz for Al/HfO<sub>2</sub>/p-Si(100) (MIS) capacitors. The HfO<sub>2</sub> films were deposited by ALD on the bare Si and chemical oxidized Si for 40 cycles followed by PDA at 500°C for 5 min in  $N_2$  ambient.

Figure 12  $I_{ds}$ - $V_{ds}$  characteristics of an NMOSFET with ~ 4 nm ALD HfO<sub>2</sub> gate dielectric and 200 nm Al gate electrode. L/W = 5 $\mu$ m/400 $\mu$ m, V<sub>g</sub> from 0 to 1.0 V with a step of 0.25V.