### Development of Reliable High-k Gate Dielectrics for Scaled MOSFETs

Anri Nakajima

Research Center for Nanodevices and Systems, Hiroshima University, Japan

This work was done in cooperation with Prof. S. Yokoyama, Dr. S. Zhu, Dr. Q.D.M. Khosru, Y. Yokoyama, H.Ishii, T. Kasai, T. Kidera, T. Yoshimoto, T. Ohashi, and Dr. H.Miyake.

# Outline

- Introduction

- Reliability study

Static bias temperature instability in plasma nitrided SiON

gate dielectrics

Bias temperature instability under high-frequency bipolar gate bias stressing in plasma nitrided SiON gate dielectrics

- · Practical application of ALD Si nitride

- · Development of ALD high-k gate dielectrics

- Summary

## Introduction

For realization of 3 dimensional-custom stack system, we need high-performance transistors.

To fabricate such transistors, one of the key issues is development of high reliable gate dielectrics.

For the development, the following subjects were studied in our group:

- ·Reliability study

- · Practical application of ALD Si nitride

- ·Development of ALD high-k gate dielectrics

## Outline

- Introduction

- Reliability study Static bias temperature instability in plasma nitrided SiON gate dielectrics

Bias temperature instability under high-frequency bipolar gate bias stressing in plasma nitrided SiON gate dielectrics

- · Practical application of ALD Si nitride

- · Development of ALD high-k gate dielectrics

- Summary

### background

Remaining problems

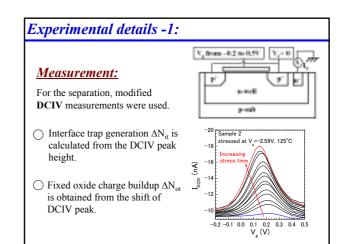

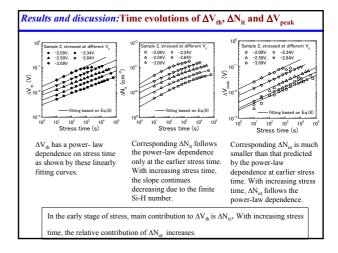

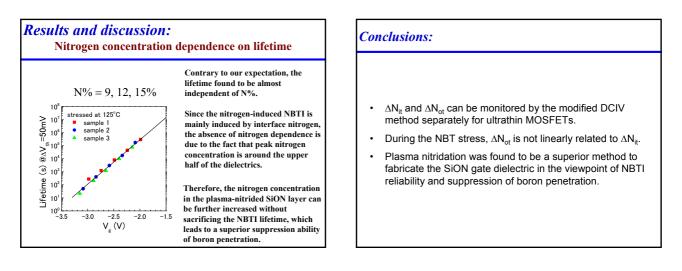

- Detail mechanism of negative BTI (NBTI) has still not fully been understood for SiON gate dielectrics.

- For plasma-nitrided gate dielectrics, quantitative impact of nitrogen concentration on NBTI has not been reported yet.

To examine the above,

• Separate evaluation of the effect of  $\Delta N_{it}$  and  $\Delta N_{ot}$  to NBTI is extremely important.

## Experimental details -2:

#### **Devices:**

- pMOSFETs with p<sup>+</sup> poly-Si gate, plasma-nitrided SiON gate dielectric.

- W/L=10 µm/2 µm.

- T<sub>ox</sub>=2.0nm, N% = 9, 12, 15%,

- EOT= 2.22, 2.17, 2.12 nm

#### Stress:

negative V<sub>g</sub>, at 125°C

other electrodes grounded

# Outline

- Introduction

- Reliability study Static bias temperature instability in plasma nitrided SiON gate dielectrics

- Bias temperature instability under high-frequency bipolar gate bias stressing in plasma nitrided SiON gate dielectrics

- · Practical application of ALD Si nitride

- · Development of ALD high-k gate dielectrics

- Summary

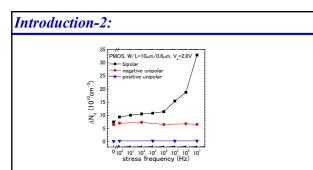

# Introduction-1:

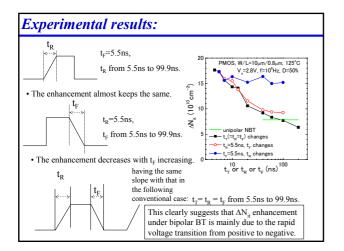

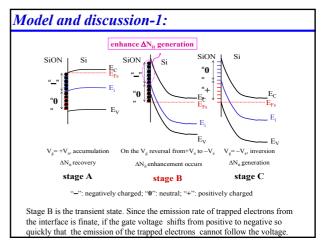

- For pMOSFET under static NBT stress, it has been known that devices were degraded at the  $V_g = -V_a$  stage, and was partially recovered at the  $V_g = 0$ or  $V_g = +V_a$  stage.

- This implies that the dynamic NBT stress may have the similar degradation with the unipolar NBT stress regardless of stress frequency.

- Indeed, under unipolar BT stress, the degradation is almost independent of frequency.

- However, under bipolar BT stress, the degradation is **enhanced** at f > 10 kHz, and is dependent of frequency.

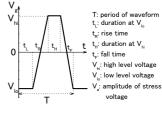

### Experimental details:

#### <u>Devices:</u>

pMOSFETs with p<sup>+</sup> poly-Si gate and plasma-nitrided SiON gate dielectrics. T<sub>ox</sub>=2.0nm, N% = 15%, EOT= 2.12 nm

#### <u>Stress:</u>

To reveal the degradation enhancement mechanism more clearly, stress pulse wave dependence on the degradation was studied in bipolar BTstress.

#### **Conclusions:**

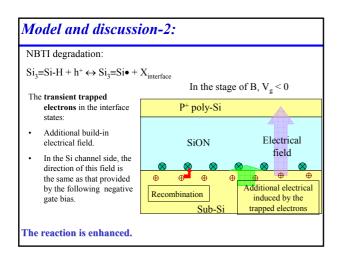

- For pMOSFET under dynamic BT stress, besides the degradation at the V<sub>g</sub> = -V<sub>a</sub> stage and recovery at the V<sub>g</sub> = +V<sub>a</sub> stage, an additional degradation occurs at the falling edge of each cycle.

- The additional degradation is proposed to arise from the trapped electrons in the transient states upon V<sub>g</sub> switching from +V<sub>a</sub> to -V<sub>a</sub> quickly.

- For reliability improvement in high frequency (such as VHF) CMOS logic operation, this waveform effect may need to be taken into account.

## Outline

- Introduction

- Reliability study

Static bias temperature instability in plasma nitrided SiON

gate dielectrics

Bias temperature instability under high-frequency bipolar

gate bias stressing in plasma nitrided SiON gate dielectrics

Practical application of ALD Si nitride

- · Development of ALD high-k gate dielectrics

- Summary

## Application of ALD Si nitride/SiO<sub>2</sub> gate dielectrics to future DRAMs

• Plasma-nitrided SiO<sub>2</sub> has been proposed as the gate dielectrics for next-generation DRAMs.

#### Problems

With scaling T<sub>ox</sub>, the low nitrogen concentration

↓ Heavy thermal budget peculiar to DRAM fabrication process Insufficient suppression of boron penetration

2. High nitrogen concentration → Degrade NBTI

New gate dielectrics for future DRAMs are desired.

# Suppression of boron penetration after high thermal budget

Since there is smallest  $V_{th}$  shift for ALD stack gate dielectrics, the stack dielectrics have a special advantage over plasma-nitrided gate SiO<sub>2</sub> and pure gate oxide as regards the suppression of boron penetration.

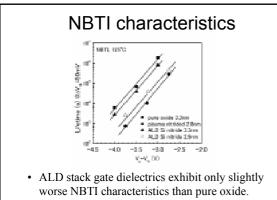

• Better NBTI characteristics were achieved than those of plasma-nitrided gate SiO<sub>2</sub>.

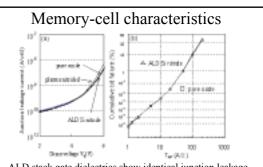

- ALD stack gate dielectrics show identical junction leakage current to that of pure gate oxide and better characteristics than the plasma-nitrided gate SiO<sub>2</sub>.

- MCs having transistors with ALD stack dielectrics show identical T<sub>ref</sub> distribution to those having transistors with pure gate oxide.

#### **Conclusions:**

• ALD stack dielectrics are a promising candidate for gate dielectrics of future high-speed and high-reliability DRAMs.

## Outline

- Introduction

- Reliability study

Static bias temperature instability in plasma nitrided SiON gate dielectrics

Bias temperature instability under high-frequency bipolar gate bias stressing in plasma nitrided SiON gate dielectrics

- · Practical application of ALD Si nitride

- Development of ALD high-k gate dielectrics

- Summary

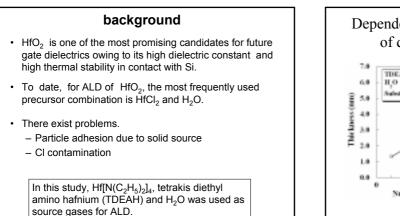

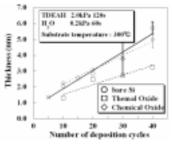

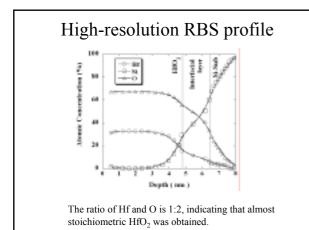

# Dependence of $HfO_2$ thickness on number of deposition cycle on Si or SiO<sub>2</sub>

The thickness varies almost linearly with cycle number.

From the slope, the deposition rate was estimated to be 0.06- 0.1 nm

The film growth follows a layer-by-layer growth kinetics.

#### **Conclusions:**

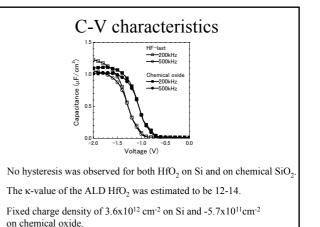

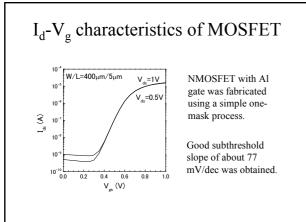

•ALD using TDEAH and  $H_2O$  is promising for high reliable high-k gate dielectrics.

# Summary

- In reliability study, we established new evaluation method and got new information.

- We showed the applicability of ALD Si nitride/SiO<sub>2</sub> stack gate dieleictrics to future DRAMs.

- We established ALD of high-k gate dielectrics.

From the veiwpoints, we developed and improved gate dielectrics for high-performance transistor.