# Metal Gate and Junction Technologies for Leading Edge Devices Kentaro Shibahara Research Center for Nanodevices and Systems, Hiroshima University 1-4-2, Kagamiyama, Higashihiroshima, 739-8527 Japan Phone +81-82-424-6267, FAX: +81-82-424-3499, e-mail: ksshiba@hiroshima-u.ac.jp

## 1. Introduction

Our COE project aims development of 3DCSS system that needs high-performance mixed-signal devices. We are working for development fundamental device technologies for such devices. Our investigation subjects are categorized to major two fields. One is shallow junction formation and another is metal-gate workfunction tuning. The former and the latter are key technologies to improve  $f_T$  and  $f_{MAX}$  by reducing parasitic source/drain resistance and gate resistance, respectively. In addition, they are core technologies for CMOS logic devices.

In this abstract, major research establishments obtained during the term of our COE project.

### 2. Metal gate technology

Gate depletion issue is one of the most important issues to be solved for improving MOSFET performance with scaling. Since the gate depletion is attributed to semiconducting nature of poly-Si gate, its replacement with metal material is the best way to remove the problem. However, it also leads to losing the benefit of workfunction tuning by doping. Since a dual gate structure is indispensable for CMOS devices, we have worked on this target for these several years [1-15].

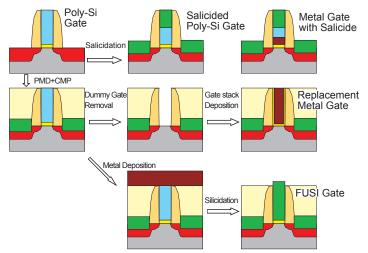

Metal gate MOS fabrication processes are categorized to several manners, as shown in Fig.1. Mo gate are suitable for conventional self-aligned gate process and replacement gate process. We have reported workfunction tuning with nitrogen incorporation into Mo [1-5]. Though workfunction tunable range was not enough for practical device application, we have indicated nitrogen pileup at the Mo/gate SiO<sub>2</sub> interface was a key to modulate workfunction value.

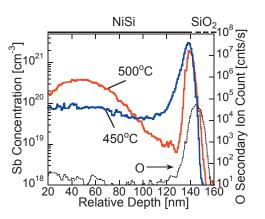

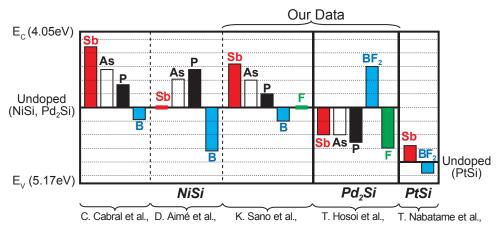

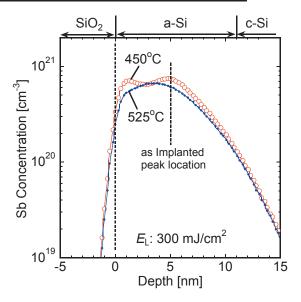

FUSI (Fully Silicided) gate process [6,7] that converts entire part of gate poly-Si to silicide by slicidation reaction, as shown in Fig. 1, is also a workfunction tuning method. Impurities introduced to poly-Si prior to the silicidation are swept out towards the gate insulator interface during the silicidation and form pileup a the interface. We have investigated the relationship between silicidation condition of NiSi FUSI gate and its workfunction [8-10]. As shown in Fig. 2, Sb pileup peak height strongly depended on the FUSI process temperature. Though motive force of Sb redistribution is segregation at the silicide/poly-Si interface, too fast silicidation at high temperature (500°C) silicidation resulted in insufficient pileup formation for workfunction modulation. Such a process condition dependence is considered to be the origin of discrepancy of workfunction tunable range between research organizations shown in Fig. 3.

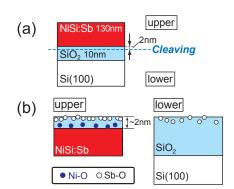

Precise location of Sb pileup was evaluated by XPS measurement [11] utilizing the feature that Sb doped specimen was cleavable at the gate oxide, as shown in Fig. 4(a). The specimen was divided to upper and lower parts, as shown in Fig. 4(b). Sb-O related signals were observed for both the upper and the lower specimens. However, other specimens which were fabricated by different conditions showed no Sb penetration [12], in spite that both specimens showed workfunction shift. This discrepancy is another example of process sensitivity of FUSI process, and it also shows workfunction shift mechanism is still an open question.

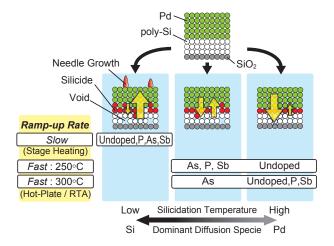

Although NiSi is the most popular material for FUSI process, we are also working on Pd<sub>2</sub>Si as an alternative candidate. Lower silicidation temperature of Pd<sub>2</sub>Si gives flexibility to device fabrication process, and higher thermal stability is also advantageous. Defect formation during FUSI process is one of the critical issues that blocks FUSI gate against practical use [8,9,11]. We have discussed slicidation mechanism of Pd<sub>2</sub>Si based on silicidation with three kinds of heating apparatuses [13-15]. It was concluded that low temperature silicidation led to defective film formation because of Si diffusion, as shown in Fig. 5. We believe that this tendency is common for NiSi FUSI. Therefore high ramp-up apparatus should be used for FUSI gate formation. It should be also noted that workfunction shift direction in Pd<sub>2</sub>Si by impurity pileup formation is quite opposite to NiSi and PtSi cases, as shown in Fig. 3. Interface structure of Pd<sub>2</sub>Si should be characterized by photoelectron spectroscopy like a NiSi case shown above for the discussion of workfunction shift mechanism.

3. Shallow Junction formation by laser annealing

Currently introduction of new generation annealing

technologies that succeed RTP are demanded for source and drain (S/D) formation of leading edge device mass production. New annealing technologies provide shallower S/D necessary for further scaling of CMOS devices. Melt laser annealing (LA) is one of such technologies. We have investigated the melt LA using KrF excimer laser [16-22,27] and solid state green laser [23-26] as a light source to heat up specimens. Among the achievements obtained through these works, proposal of partial-melt LA (PMLA) is the most notable one.

The words "melt LA" currently stand for LA that utilizes melting point difference between crystalline Si and amorphous Si. Selective melting of a thin amorphous Si layer whose melting point is lower than crystalline by about 300°C suppresses over-melt to crystalline Si and leads to high activation due to non-equilibrium re-crystallization. Ge<sup>+</sup> implantation prior to dopant implantation is usually used for the a-Si layer formation.

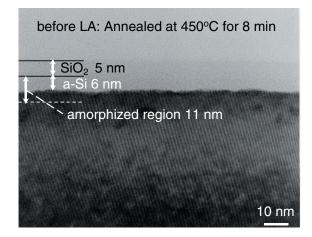

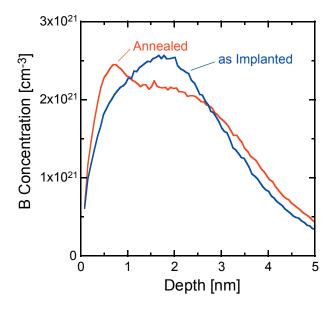

We have proposed the combination of substrate heating and LA, that is heat-assisted LA (HALA) [16-18]. Although this method reduced necessary laser energy density to obtain good dopant activation, basic idea is common to the ordinary melt LA. We have added solid-phase regrowth process prior to laser irradiation. It was the proposed new LA scheme, that is, PMLA. By performing pre-annealing for appropriate duration, amorphous layer thinner than initial thickness can be obtained, as shown in Fig. 6. The a-Si thinning enbales melting shallower than initial a-Si depth, as shown in Fig. 7. PMLA is usable together with HALA. By this, PMLA obtain features which are preferable to shallow junction formation, as shown in Table I. We have demonstrated PMLA with 10-nm B-doped junction formation [20,21]. Sheet resistance about 700 $\Omega$ /sq. was obtained for 10 nm junctions with negligible diffusion, as shown in Fig. 8. Please note that Fig. 8 was plotted in a linear scale to emphasis redistribution of B.

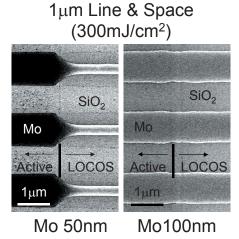

We have mainly investigated annealing method without combining it with device fabrication processes. However, introduction of new process to fabrication flow is often suffered by difficulties. In the case of LA, gate electrode deformation in isolation region, shown in Fig. 9, is typical one. To overcome such a issue, thermal diffusion analysis of annealing process should be utilized in addition to experimental approach [22,25,27].

### 4. Summary

Notable topics on workfunction tunable metal gate technology and melt LA technologies obtained through our COE project are summarized. Each of these technology has long research history. However, both technologies still have a lot of issues to be solved before practical use. Therefore, trial to brush up technologies and explain process mechanisms should be continued.

#### Acknowledgements

Our research activities were partly supported by STARC and NEDO/MIRAI Project. The research achivement shown here is a result of cooperative work with co-authors for publications listed below.

#### References

1. T. Amada et al., MRS Proc., 716 (2002) pp. 299-314.

2. K. Shibahara, Ext. Abst. of 1st. Hiroshima Int. Workshop on NTIP, 2003, pp. 38-39.

3. M. Hino et al., Ext. Abst. Int. Conf. SSDM 2003, pp. 494-495.

4. K. Sano et al., Ext. Abst. of 2nd. Hiroshima Int. Workshop on NTIP, 2004, pp. 58-59.

5. T. Hosoi et al., Abst. of MRS 2005 spring meeting, pp.191-192.

6. K. Shibahara, Proc. Int. Symp.on VLSI Tech., Sys. and Applications., 2006, pp. 105-106, Invited.

7. K. Shibahara, Ext. Abst. of 4th Hiroshima Int. Workshop on NTIP, 2005, pp. 82-83.

8. K. Sano et al., Ext. Abst. Int. Conf. SSDM 2004, pp. 456-457.

9. K. Sano et al., Jpn. J. Appl. Phys. 44, pp. 3774-3777 (2005).

10. T. Hosoi et al., Ext. Abst. 3rd Hiroshima Int. Workshop on NTIP, 2004, p. 70-71.

11. T. Hosoi et al., Int. Semiconductor Device Res. Symp. Proc., 2005, pp. WP-4-05-1-WP-4-05-2.

12. A. Ohta et al., Ext. Abst. Int. Conf. SSDM, 2006, pp. 216-217.

13. K. Sano et al., Proc. 13th Int. RTP Conf., 2005, pp.145-148.

14. T. Hosoi et al., Ext. Abst. Int. Conf. SSDM, 2006, pp. 218-219.

15. T. Hosoi et al., Jpn. J. Appl. Phys. 46, (2007) accepted for publication.

16. K. Kurobe et al., Ext. Abst. IWJT, 2002, pp.35-36.

17. K. Kurobe et al., Proc. of 3rd Hiroshima Int. Workshop on NTIP, 2004, pp. 74-75.

18. K. Kurobe et al., Jpn. J. Appl. Phys. 44, pp. 8391-8395 (2005).

19. K. Shibahara et al., Ext. Abst. IMFEDK, 2005, pp. 135-136.

20. K. Shibahara, Ext. Abst. IWJT, 2005, pp. 53-54, Invited.

21. K. Shibahara et al., IEEE Trans. Electron Devices **53**, pp. 1059-1064 (2006).

22. A. Matsuno et al. Jpn. J. Appl. Phys. 45, pp.8537-8541 (2006).

23. E. Takii et al., Abst. Int. Conf. on Ion Implantation Tech., 2004, p. 63.

24. E. Takii et al., Jpn. J. Appl. Phys. Part 2. Letter 44, pp. L756-L759 (2005).

25. A. Matsuno et al., Nucl. Instr. and Meth. B 237, pp. 136-141 (2005).

26. A. Matsuno et al., Ext. Abst. Int. Conf. SSDM, 2005, pp.914-915.

27. K. Shibahara, Proc. Int. Symp.on VLSI Tech., Sys. and Applications., 2006, pp. 50-51.

Fig. 1 Fabrication process flow and schematic cross section of MOSFETs for various gate materials.

Fig. 3 Summary of the workfunction shift with various impurities in NiSi, PtSi, and Pd,Si FUSI gate MOS structures.

Fig. 4 (a) Sample structure for XPS measurement shown in Fig. 8. The specimen was cleaved and divided to upper and lower pieces. (b) A model to show the location of Sb pileup.

Fig. 5 Schematic model of silicide formation under various silicidation conditions. Silicidation temperature, its ramp-up rate and the presence of impurities affect the kinetics of silicide formation due to the change of dominant diffusion species.

Table I. Comparison of features for various laser annealing schemes.

| Method            | Laser Energy<br>Density | Sheet<br>Resistance | Junction<br>Depth |

|-------------------|-------------------------|---------------------|-------------------|

| Melt              | High                    | Low                 | > as I.I.         |

| non-Melt          | Low                     | High                | ~ as I.I.         |

| Partially-Melt    | High                    | ?                   | ~ as I.I.         |

| Partially-Melt+HA | Low                     | Low                 | ~ as I.I.         |

Fig. 6 XTEM image before laser irradiation. The specimen was heated for 8 min. Lower half of amorphized layer recrystallized by the heating.

Fig. 7 Sb depth profiles after HALA. The profiles for the heatassist of 450°C shows two peaks because of partial melting of amorphized region. Profile for 525oC was considered to be a result of non-melt LA because of absence of a-Si layer due to faster re-crystallization rate at higher temperature.

Fig. 8 B profiles before and after PMLA with heat-assist at 450°C. Diffusion in a tail region is much smaller than 1 nm.