## **Development of Fabrication Processes for New SOI MOS Transistor and a** Silicidation Technique for Source and Drain of Vertical Channel Devices

Kiyoshi Okuyama, Koji Yoshikawa, Shunpei Matsumura, Atsushi Sugimura and Hideo Sunami

Research Center for Nanodevice and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan Phone: +81-82-424-6265, Fax: +81-82-424-3499, E-mail: okuyama@sxsys.hiroshima-u.ac.jp

### 1. Introduction

Three-dimensional (3-D) devices have been investigated for further scaled devices [1-2]. While, these devices have certain possibilities to realize various functions in future LSI. From this viewpoint, a new functional 3-D device has been developed and a silicidation technique of source and drain for 3-D structure devices has been investigated.

#### 2. Development of a new SOI MOS transistor

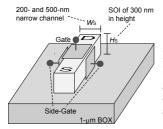

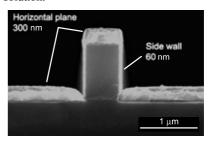

Suppression of stand-by power is one of the key issues on VLSI circuits. Therefore, it has been studied to control the threshold voltage of MOSFET by various substrate biasing [3]. For a case of multi-gate devices, there is certain possibility to control device characteristics for respective device independently [4]. From this viewpoint, a narrow-channel SOI MOSFET with additional side-gate electrodes as shown in Fig. 1 is fabricated and investigated its subthreshold behavior [5].

A narrow-channel Fig. 1 SOI MOSFET with additional gate electrodes. These gates are formed on both sides of an SOI channel.

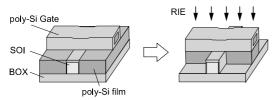

A key fabrication process is shown in Fig. 2. After formation of SOI channel of 300 nm in height by RIE and deposition of poly-Si film, subsequent leveling is achieved by CMP. Gate electrode is formed on this surface and covered with its own thermal oxide. Additional side electrodes are delineated by RIE with SiO<sub>2</sub>-covered gate as an etching mask.

Fig. 2 A key fabrication process of the device. A gate electrode is formed on CMP etch-backed surface. Sidewall gates are formed subsequent RIE by using the top gate electrode as an etching mask.

Fig. 3 An SEM image of fabricated gate structure. Additional-side-gate electrodes are successfully formed on both sides of the narrow SOI channel.

An SEM image for this structure is illustrated in Fig. 3. Subsequent source and drain formation is achieved by arsenic ion implantation and subsequent rapid thermal annealing. Gate oxide thicknesses are 4.7 nm for top one and 4.8 nm for additional side ones.

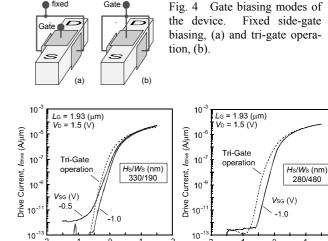

The device can be operated not only on fixed side gate biasing but also as tri-gate transistor shown in Fig. 4.  $I_{\rm D}$ - $V_{\rm G}$  characteristics on these operations of devices with 190/330 and 480/280 in ratio of channel width and height,  $H_{\rm S}/W_{\rm S}$  are shown in Fig. 5.

0

Gate Voltage, VG (V)

(a)

-1

Fig. 5 Experimental  $I_{\rm D}$ - $V_{\rm G}$  characteristics of the device. Improvement of subthreshold behavior by side-gate biasing and variation of threshold voltage are observed.

-2

-1

0

(b)

Gate Voltage, VG (V)

2

2

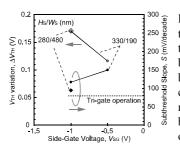

Improvement of subthreshold-current characteristics by side gate biasing and threshold-voltage variations between operation modes are observed. These are summarized in Fig. 6. An S-parameter is 79.8 mV/decade on tri-gate operation for both devices and varies from 95 to 150 mV/decade for fixed- $V_{SG}$  opera-Threshold-voltage variation from that of tion. tri-gate operation,  $\Delta V_{\rm TH}$  achieves 170 mV at  $V_{\rm SG}$  = -1.0 V for both of devices though these S-parameters

are held at 95 and 117 mV/decade, respectively. Threshold-voltage variations are achieved in response to performance requirement.

Fig. 6 Dependence of thereshold voltage and subthreshold slope on side-gate biasing.  $V_{\text{TH}}$  is defined to be gate voltages at drive currents achieve at 100 nA/µm and  $\Delta V_{\text{TH}}$  defined to be  $V_{\text{TH}}$  difference from that of tri-gate operation.

# 3. A silicidation technique for source and drain of vertical channel transistor

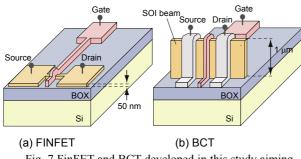

3-D transistors, e.g. FinFET, have been extensively developed for further scaled devices. While, beamchannel transistor, BCT with tall vertical Si channel shown in Fig. 7(b), have been developed aiming planer-area conscious driving current [6, 7]. Although, there are some issues because of its high-aspect-ratio structure.

Fig. 7 FinFET and BCT developed in this study aiming planer-area conscious driving current.

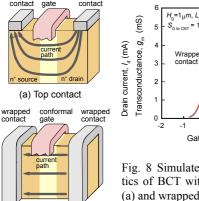

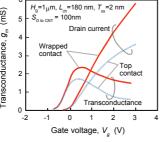

Figure 8 shows simulated  $I_D$ - $V_G$  characteristics of BCT with different two contact structures [8]. For tall vertical-channel transistors, usual top-contact structure causes decrease of driving current. Silicidation of source and drain provides a solution to this problem. From this viewpoint, silicidation process for vertical-channel device is investigated.

conformal top

top

(b) Wrapped contact

Fig. 8 Simulated  $I_D$ - $V_G$  characteristics of BCT with usual top contact, (a) and wrapped contact, (b).

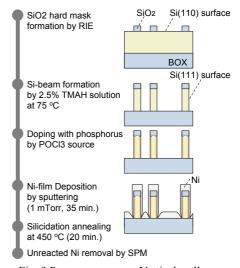

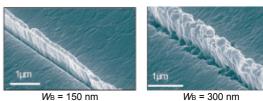

Process sequence is shown in Fig. 9. Beams having steep vertical walls are formed on (110) SOI using tetra-methl-ammonium-hydroxide, TMAH. Ni films are deposited by sputtering. Directionality of the sputtering causes deposition-rate difference between horizontal and vertical surfaces as shown in Fig. 10.

Fig. 9 Process sequence. Vertical walls are formed on (110) SOI using tetramethl-ammonium-hydroxide, TMAH solution.

Fig. 10 An SEM image of deposited Ni film on vertical Si wall by sputtering method.

Silicidation annealing is implemented in deposition chamber at 450 °C. In this case, deformation of Si beams is observed as shown in Fig. 11. It is noted that wider beams are more deformed.

Fig. 11 Bird's eye views of Si beams silicided in deposition chamber at  $450 \,^{\circ}$ C.

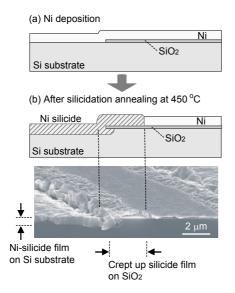

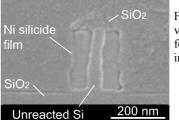

To investigate its reaction mechanism, Ni film is deposited on SiO<sub>2</sub>-patterned Si-substrate and is annealed 20 minutes at 450 °C. Ni-silicide film creeps up on SiO<sub>2</sub> as shown in Fig. 12. Its crept-up length from the edge of SiO<sub>2</sub> patterns is almost 2  $\mu$ m although silicide film on Si-substrate is less than 500 nm in thickness [9].

From these results, it is understood that deformation of beams is caused by Si-diffused reaction to unreacted Ni-films on  $SiO_2$ . To avoid this, control of annealing condition is needed.

Fig. 12 Crept-up silicide on  $SiO_2$  film. Its length from the edge of patterns is almost 2  $\mu$ m.

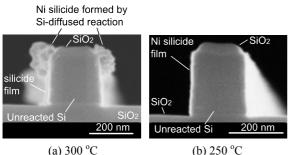

Figure 13(a) shows an SEM image of a Si beam silicided by in-situ annealing at 300 °C. 55-nm-thick Ni-silicide film is formed on the sidewall, but silicide formed by Si-diffused reaction is observed. For the case of 250-°C annealing shown in Fig. 13(b), deformation caused by Si diffution is suppressed and 30-nm-thick silicide film is formed.

(a) 300 C (b) 250 C Fig. 13 Silicided beams formed at 300 °C and 250 °C. In the former condition, Ni silicide formed by Si-diffused reaction is observed.

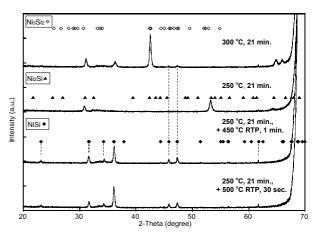

XRD spectrums for these samples are shown in Fig. 14.  $Ni_3Si_2$  phase is observed as a dominant at 300-°C-annealing case, but deformation of Si-beam is occurred in this case. For 250-°C-annealing case, more Ni richer film, Ni<sub>2</sub>Si phase is detected, and deformation of Si-beam caused by Si-diffused reaction is not observed. After annealing at 250 °C and unreacted Ni removal by SPM, NiSi film is obtained by rapid thermal anneling at 450 or 500 °C avoiding Si-beam deformation.

Fig. 14 XRD spectrums of silicided samples annealing at 300 and 250 °C and 2-step annealing.

Figure 15 shows an SEM image of a silicided beam by 2-step annealing process. 60-nm-thick NiSi film is uniformly formed on the sidewall without abnormal deformation of Si-beams.

A silicidation process for vertical structure device is discussed. For cases of annealing at 300 °C or more, Si-diffused reaction causes deformation of beams. 2-step annealing process prevents this phenomenon and NiSi film is successfully formed on vertical walls.

Fig. 15 A cross-sectional view of Ni-silicided beam formed by 2-step anneal-ing process.

Officacted St

### 4. Summary

In this paper, development of a new functional 3-D device and a silicidation technique of source and drain for 3-D structure devices have been discussed.

An SOI nMOSFET with additional side gate electrodes is fabricated and discussed its subthreshold behaviors. Threshold-voltage variations are achieved in response to performance requirement. In the viewpoint of stand-by-power suppression, these provide certain controllability to circuit operation.

In the silicidation process for vertical structure device, Si-diffused reaction causes deformation of Si-beams in cases of annealing at 300 °C or more. A 2-step annealing process prevents this phenomenon and NiSi film is successfully formed on vertical walls.

### Acknowledgements

This work has been supported in part by a Grant-in-Aid for the 21st Century COE program "Nanoelectronics for Tera-bit Information Processing" from the Ministry of Education, Science, Sports and Culture of Japan.

### References

- Y-K. Cho, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Andersen, T-J. King, J. Bokor, and C. Hu, IEDM Tech. Dig., pp. 421-424, 2001.

- [2] B. Doyle, B.Boyanov, S.Datta, M. Doczy, S. Hareland, B.Jin, J. Kavalieros, T. Linton, R.Rios, and R.Chau, Symposium on VLSI Technology Digest of Technical Paper, 2003.

- [3] T. Kuroda, T. Fujita, S. Mita, T. Nagamatsu, S. Yoshioka, K. Suzuki, F. Sano, M. Norishima, M. Murota, M. Kako, M. Kinugawa, M. Kakumu, and T. Sakurai, IEEE JSSC, 31, pp. 1770-1779, 1996.

- [4] Y. X. Liu, M. Masahara, K. Ishii, T. Tsutsumi, T. Sekigawa, H. Takashima, H. Yamauchi, and E. Suzuki, IEDM Tech. Dig., pp. 986-988, 2004.

- [5] K. Okuyama, Yoshikawa, and H. Sunami, Ext. abs. SSDM Ext. Abs. pp.506-507, 2006.

- [6] A. Katakami, K. Kobayashi, and H. Sunami, Jpn. J. Appl. Phys., Vol. 42, Part 1, No. 4B, pp. 2100-2105, 2004.

- [7] T. Furukawa, H. Yamashita, and H. Sunami, Jpn. J. Appl. Phys., Vol. 43, No. 4B, pp. 2145-2150, 2003.

- [8] DESSIS, ISE TCAD, release 9.5, Synopsys Co., Ltd

- [9] S. Matsumura, A. Sugimura, K. Okuyama, and H. Sunami, Advanced Metallization Conference 2006: 16th Asian Session Sept. 25-27, 2006.