Research Center for Nanodevices and Systems (RCNS) System Design and Architecture Research Division

## A Human-memory Based Learning Model and Hardware Prototyping in FPGA

A. Ahmadi, M.A. Abedin, H.J. Mattausch, T. Koide, Y. Shirakawa, and M.A. Ritonga Research Center for Nanodevices and Systems, Hiroshima University

Optimization includes a dynamic process for updating of reference patterns magnitude as well as distance thresholds by using the data of coming input samples and taking an averaging technique.

Updating Steps:

1- Updating Ranks

(ranks are used to control the life-time of each Ref. pattern in the memory)

2- Updating Ref. Pattern magnitude (used for optimizing the classification)

3- Updating Distance Thresholds ( $D_{th}$ ) (used to optimize the classification reliability as well as generation of new Ref. patterns)

8

#### **Associative Memory Model**

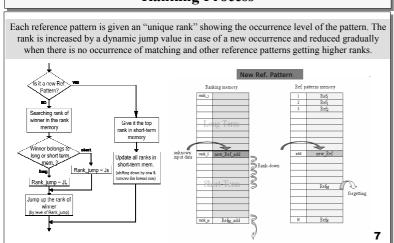

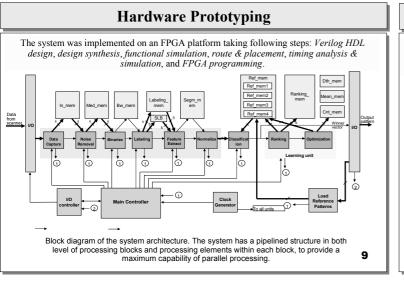

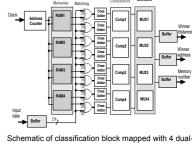

As for implementation of classification block and in order to model the fully-parallel functionality of the associative memory to be used as the main classifier of the system, we applied four dual-port SRAM memory blocks each contains 32 data words in the FPGA.

designed as an LSI chip.

Schematic of classification block mapped with 4 dualport RAM blocks in an FPGA architecture. 16 matchings are performed within one clock cycle. 10

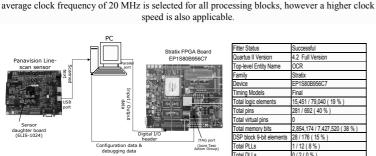

An Altera Stratix family FPGA device (EP1S80) is applied for hardware prototyping

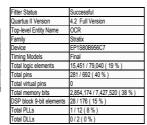

Resource usage for the whole system including preprocessing (excepting feature extraction), classification, and learning blocks, implemented in an Altera Stratix FPGA. 11

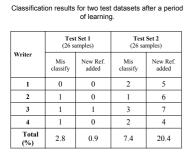

### **Experimental Results: Classification (2)**

**FPGA Programming**

The whole system was fitted into an FPGA platform without need to external resources. An

The average misclassification rate is around 5% which is reasonable for this type of application

#### **Experimental Results: Classification (1)**

The system performance was evaluated by using real data samples. A number of 35 datasets (832 samples) of English characters written by four different writers were used for the experiments.

450

40 350

100

The number of patterns added as new references as well as the misclassification rate is high in the beginning of the process but when the learning goes on and system adjusts continuously the reference pattern memory and distance 12 thresholds, the misclassification rate reduces dramatically.

Total

(%)

197 73.6 197 43.8 24 38.9 22.1

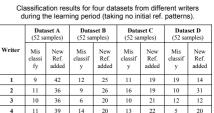

# **Experimental Results: Learning** Results of Learning speed Distance

By learned pattern we refer to reference pattern which is already entered in the long-term memory. In approach 1 all the ew Ref. patterns are entered in the short-tem memory first, while in approach 2 if the long-term memory is not yet full, the new Ref. pattern will be located in an unoccupied address of long-term memory.

14

400

37

#### Conclusions

- · A learning model based on a short/long-term memory and an optimization algorithm for constantly adjusting the reference patterns was proposed.

- The whole system blocks excepting feature extraction part were implemented in an FPGA platform and system performance was evaluated with a simulation program using real data of handwritten characters.

- In order to enhance the search speed in the classification block, we are planning to use a fully parallel associative memory implemented in an LSI architecture, as the main classifier of the system.

- · Comparing to other learning models, however this prototype model is not yet robust enough but is advantageous in terms of a simple learning algorithm, high classification speed, and a hardware-friendly structure.

15