## Circuit Design of a Single-chip Ultra-Wideband Receiver using Silicon Integrated Antennas

## Nobuo Sasaki, Masashi Fukuda, Masakazu Nitta, Kentaro Kimoto and Takamaro Kikkawa

Research Center for Nanodevices and Systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima, 739-8527 Japan E-mail: {nsasaki, kikkawa}@sxsys.hiroshima-u.ac.jp

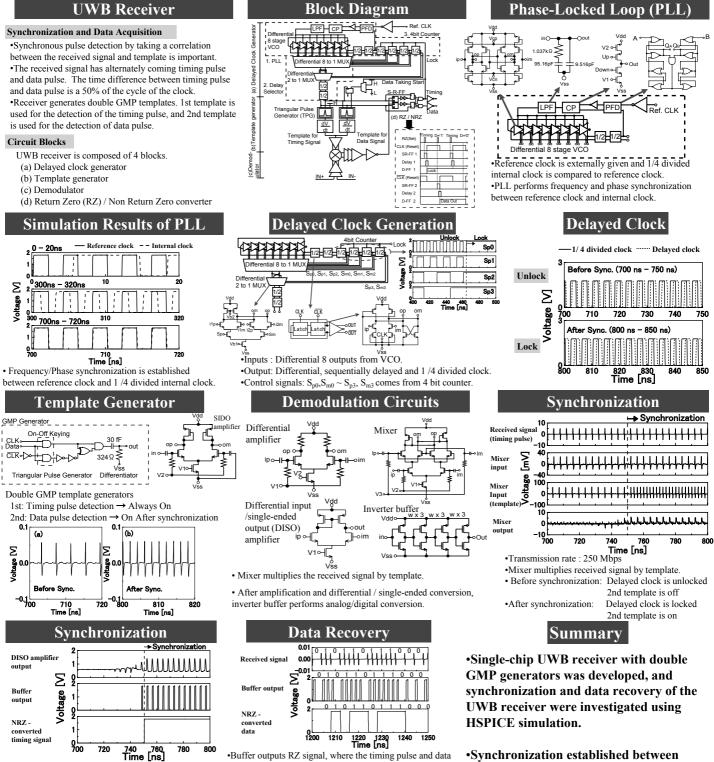

•The synchronization establishes around 750 ns. •NRZ-converted timing signal is used as a flag of the establishment of synchronization, i.e., the signal locks delayed clock.

•NRZ-converted timing signal is also used as a start signal of data acquisition.

received signal and template signal. The

the received signal, which is composed of

timing pulse and data pulse.

receiver could recover 250 Mbps data from

•After RZ / NRZ converters, timing pulse and data pulse are separated and converted to NRZ.

•The receiver is succeeding in the recovery of data from alternately coming timing pulse and data pulse. In this simulation, obtained data rate is 250 Mbps.

pulse is not separated. A fter  $\mathbf{RZ} / \mathbf{NRZ}$  converters, timing pulse and data pulse are