# Atomic-Layer-Deposition of HfO<sub>2</sub> on Si and Ge Substrates from Hafnium Tetrakis(diethylamino) and Water

Shiyang Zhu and Anri Nakajima

Reserach Center for Nanodevices and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima, Hiroshima 739-8527, JAPAN,

Phone: 81-82-4246265, Fax: 81-824243499, E-mail: zhu@sxsys.hiroshima-u.ac.jp

## Abstract

Almost stoichiometric hafnium oxide (HfO<sub>2</sub>) thin films were deposited by atomic layer deposition (ALD) from tetrakis(diethylamino)hafnium (termed as TDEAH) and water on both Si and Ge substrates. The deposition rate was estimated to be 0.9 - 0.10 nm/cycle on both Al/ALD-HfO<sub>2</sub>/p-Si substrates. capacitors have comparable electrical properties with respect to recently reported data, and MOSFETs with the ALD-HfO<sub>2</sub> gate were demonstrated. Al/ALD-HfO<sub>2</sub>/p-Ge dielectrics capacitors exhibit large hysteresis and frequency dependency in capacitance -voltage characteristics and large gate leakage current.

# **1. Introduction**

With aggressively downscaling of MOSFET feature size, the conventional SiO<sub>2</sub> based gate dielectrics will be insufficient due to excessive gate leakage current. Materials with high dielectric constant (high-ĸ), which allow us to increase the physical thickness while keeping the equivalent oxide thickness (EOT) constant, should be introduced to effectively reduce the gate leakage current. HfO<sub>2</sub> is one of the most promising candidates owing to its high dielectric constant and relatively high thermal stability with respect to Si surface [1]. Among various techniques proposed to deposit HfO2 ultrathin film, atomic layer deposition (ALD) is considered to be a promising method [2-7] because of its excellent ability to control thickness. So far, in the ALD of HfO<sub>2</sub>, the most frequently used precursor combination is  $HfCl_4 + H_2O$ . However, it suffers from the serious drawback of residual Cl contamination, which is difficult to be completely removed in the following process [2,3]. The problem can be avoided using Hf(O-t-C<sub>4</sub>H<sub>9</sub>)<sub>4</sub> precursor, but a relatively thick SiO<sub>x</sub> interfacial layer may be formed owing to the presence of O atoms in the Hf precursor [4]. Hafnium alkylamides (i.e.,  $Hf[N(CH_3)_2]_4,$  $Hf[N(CH_3)(C_2H_5)]_4$ , and  $Hf[N(C_2H_5)_2]_4$  (termed as TDEAH)), which are free of both Cl and O atoms, have been proposed as a Hf precursor recently [5-8]. Using Hf[N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>)]<sub>4</sub> and O<sub>3</sub>, high-quality ultrathin HfO<sub>2</sub> films have been obtained by Kamiyama [5] and Kirsch [6]. Moreover, Hino found that  $Hf[N(C_2H_5)_2]_4 + H_2O$  is the best combination by comparing  $Hf[N(CH_3)_2]_4$  and  $Hf[N(C_2H_5)_2]_4$  as Hf precursors and  $O_2$  and  $H_2O$  as oxidants [7]. The dependence of  $Hf[N(C_2H_5)_2]_4 + H_2O$  ALD growth on Si surface condition was also reported very recently[8].

On the other hand, enhancement of channel mobility is necessary to improve the MOSFET performance. Ge MOSFETs have been extensively studied recently as they can offer 2-fold higher electron mobility and 4-fold higher hole mobility as compared with conventional Si MOSFET theoretically [9-14]. However, due to lack of stable native oxide for Ge surface passivation, the quality of high-k dielectrics deposited on Ge is not as good as that on Si, and the kinetics of ALD growth of high-k films on Ge may also differ from that on Si. So far, various dielectrics, such as germanium oxynitride, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, have been investigated for Ge MOSFETs. However, their quality has not been satisfied as they usually exhibit large hysteresis and large gate leakage current [9-15]. Fabrication of high quality gate dielectrics on Ge is one of the key issues for the Ge MOSFET technology.

In this study, ALD growth of  $HfO_2$  on both Si and Ge substrates was investigated by the alternate exposure of TDEAH and water. MOSFETs with the ALD  $HfO_2$  gate dielectrics were demonstrated using a simple one-mask fabrication process. ALD of Si nitride on Ge using SiCl<sub>4</sub> and NH<sub>3</sub> precursors was also presented for comparison.

## 2. ALD film growth and MOSFET fabrication

A home-made ALD system is used to deposit HfO<sub>2</sub>. After cleaning, the wafer was immediately loaded into a cold-wall chamber where it was heated using a halogen lamp. TDEAH exposure followed by H<sub>2</sub>O exposure was cyclically repeated 5 – 40 times. The vapor pressure and exposure time of TDEAH were 2.0 kPa and 120 s, respectively, and those of H<sub>2</sub>O were 0.2 kPa and 60 s, respectively. The substrate temperature (T<sub>sub</sub>) kept at  $300^{\circ}$ C. All parameters, such as gas pressure, temperature, exposure time, etc., can be modified independently. For ALD of Si-nitride films, SiCl<sub>4</sub> exposure followed by NH<sub>3</sub> exposure was cyclically repeated [16].

For Si substrates, the wafers were first dipped in a 0.5% HF solution to eliminate the native oxide. Then, two different Si surface conditions are prepared: asformed bare Si (terminated with hydrogen) and chemically oxidized Si formed by dipping in a  $H_2O_2$  solution (terminated with hydroxide). After ALD growth, in-situ post deposition annealing (PDA) procedure was performed in N<sub>2</sub> ambient at 500°C for 5 min. For electrical characterization, metal-insulator-semiconductor (MIS) capacitors were fabricated by Al top electrode deposition using thermal evaporation through a shadow mask. The backside of wafer was also deposited with a thick Al film after removing oxide using the diluted HF solution to form the ohmic contact.

For simplification, MOSFETs with the ALD  $HfO_2$  gate dielectrics were fabricated using a simple one-mask process, where Al gate electrode and AsH<sub>3</sub> ion implanted source/drain were adopted.

For Ge substrates, the wafers were treated by DHF dipping before loading into the ALD chamber. The MIS capacitors were fabricated using the same process as that for Si MIS capacitors.

#### 3. Results and Discussion

## 3.1 ALD HfO<sub>2</sub> on Si substrate

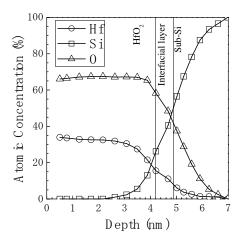

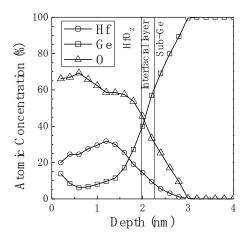

The film thickness of deposited HfO<sub>2</sub> thickness was measured using a spectroscopic ellipsometer. To minimize the fitting parameters, a one-layer simulation model is used. Therefore, the extracted thickness includes a thin interfacial SiO<sub>x</sub> layer. For both bare and chemically oxidized Si surfaces, the deposition rate of HfO2 is estimated to be about 0.10 nm/cycle from the dependence of HfO<sub>2</sub> thickness on cycle number and no incubation period at the beginning cycles was observed. In both cases, stoichiometric HfO<sub>2</sub> films were formed, as confirmed by high-resolution Rutherford backscattering spectroscopy (RBS). Fig. 1 shows depth distributions of atomic concentrations extracted from RBS for HfO2 deposition on bare Si for 40 cycles at 300°C followed by PDA in N<sub>2</sub> ambient at 500°C for 5 min. Here, the surface of the HfO<sub>2</sub> film is taken at 0 on the transversal axis. The interface of the HfO<sub>2</sub>/interfacial-SiO<sub>x</sub>-layer is defined as the position where the amount of Hf becomes half of the maximum value of the amount of Hf (4.2 nm on the transversal axis), and that of the interfacial-SiO<sub>x</sub>layer/sub-Si as the position where the amount of O becomes half of the maximum value of the amount of O (4.9 nm on the transversal axis). According to the definition, the thicknesses of the HfO<sub>2</sub> film and interfacial  $SiO_x$  layer are estimated to be 4.2 nm and 0.7 nm, respectively. The ratio of Hf and O is 1:2 up to a depth of 4 nm, indicating that the HfO<sub>2</sub> film above the interfacial layer is almost stoichiometric. The interfacial layer has a relatively high Hf content due to diffusion of Hf into the SiO<sub>2</sub> film (very thin native SiO<sub>2</sub> before deposition). For ALD HfO<sub>2</sub> on the chemically oxidized Si surface, almost similar RBS result was observed (not shown here).

Surface morphologies before and after  $HfO_2$  deposition were measured using atomic force microscopy (AFM). The roughness (rms) within 50 nm × 50 nm area of the ALD  $HfO_2$  film is about 0.036 nm, only slightly larger than that before deposition (0.026 nm). The  $HfO_2$

films deposited on the chemical oxidized surface have similar smooth surfaces. The smooth surface indicates the layer-by-layer growth kinetics of the  $HfO_2$  film.

Fig. 1 High-resolution RBS profile of ALD  $HfO_2$  film deposited on bare Si for 40 cycles at 300°C, after PFA in  $N_2$  ambient at 500°C for 5 min.

The absence of incubation periods and smooth  $HfO_2$  surface let us propose the following reaction during the exposure in TDEAH ambient.

$Hf(OH)_3^* + 3Hf[N(C_2H_5)_2]_4 \rightarrow$

Hf-3{O-Hf[N( $C_2H_5$ )<sub>2</sub>]<sub>3</sub>}\* + 3HN( $C_2H_5$ )<sub>2</sub>

Here, a sterisk represents the surface condition. This reaction automatically stops when all the OH groups on the surface react with TDEAH. On the other hand, during the subsequent  $H_2O$  exposure, the following reaction occurs.

Hf-O-Hf[N(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>]<sub>3</sub><sup>\*</sup> + 3H<sub>2</sub>O  $\rightarrow$ Hf-O-Hf(OH)<sub>3</sub><sup>\*</sup> + 3HN(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>

This reaction also automatically stops when all the  $N(C_2H_5)_2$  groups on the surface react with  $H_2O$ . As a result, approximately one monolayer is formed per cycle because the reported interatomic distance is between 0.208 and 0.219 nm for the Hf-O bonds of HfO<sub>2</sub> [17].

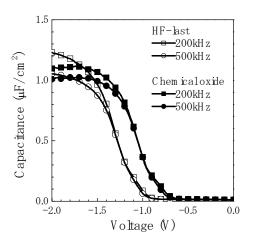

Figure 2 shows the capacitance-voltage (C-V) characteristics for HfO2 deposited on the bare Si and on the chemically oxidized Si measured at 200 and 500 kHz. No hysteresis (or less than 1 mV) was observed for both samples, whereas the accumulation capacitance has a slight decrease when frequency increasing from 200 to 500 kHz probably due to the large capacitor area  $(2 \times 10^{-4})$ cm<sup>2</sup>). The EOTs were determined from the 200 Hz accumulation capacitance to be 2.09 and 2.29 nm for HfO<sub>2</sub> on base-Si and that on chemically oxidized Si, respectively, after quantum-mechanical correction. The  $\kappa$ -value of the ALD HfO<sub>2</sub> was estimated to be 12 – 14, comparable to some reports for the ALD HfO<sub>2</sub> [18,19]. Taking the extracted flat-band voltages (V<sub>fb</sub>) and Al work function (-0.91 V) into account, the fixed charge densities in the dielectric were estimated to be  $3.6 \times 10^{12}$  $\text{cm}^{-2}$  for the bare-Si sample and  $-5.7 \times 10^{11} \text{ cm}^{-2}$  for the chemical oxidized sample. The lower fixed charge

density of the chemically oxidized sample indicates its better interfacial quality.

Fig. 2 Capacitance-voltage curves measured at 200 and 500 kHz for Al/HfO<sub>2</sub>/p-Si(100) (MIS) capacitors. The HfO<sub>2</sub> films were deposited by ALD on the bare Si and chemical oxidized Si for 40 cycles followed by PDA at  $500^{\circ}$ C for 5 min in N<sub>2</sub> ambient.

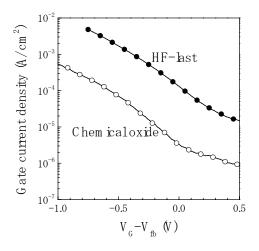

The gate leakage current is shown in Fig. 3 as a function of  $V_G - V_{fb}$  for both samples. The leakage at  $V_G - V_{fb} = -0.6$  V is about  $2.5 \times 10^{-3}$  A/cm<sup>2</sup> for the bare-Si sample and  $1.2 \times 10^{-4}$  A/cm<sup>2</sup> for the chemically oxidized sample, which are consistent with the EOTs. Compared with the theoretical leakage current of SiO<sub>2</sub> with the same EOT, our HfO<sub>2</sub> film offers a leakage current reduction of about 1 - 2 orders of magnitude. The leakage current of our Al/ALD-HfO<sub>2</sub>/SiO<sub>x</sub>/Si MIS capacitors is comparable to that from recently reported data using a similar gate electrode [18-20]. It is expected that the leakage current may be further reduced by optimizing the gate electrode formation and reducing the MIS area [5].

Fig. 3 Gate leakage current density versus  $V_G$  -  $V_{fb}$  for two Al/HfO<sub>2</sub>/p-Si MIS capacitors, as in Fig. 2

#### 3.2 MOSFETs with ALD HfO<sub>2</sub> gate dielectrics

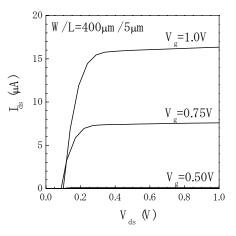

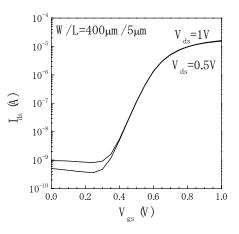

A simple one-mask process was used to fabricate MOSFET. The starting wafer is p-Si(100) with resistivity of 8–9  $\Omega$ ·cm. After DHF dipping, approximately 4 nm HfO<sub>2</sub> film was deposited by ALD for 40 cycles. Then approximately 200 nm thick Al film was deposited using followed thermal evaporation, by conventional procedures as photolithography, wet etching, and AsH<sub>3</sub> ion implantation with dose of  $4 \times 10^{15}$  cm<sup>-2</sup> and energy of 30 keV. Finally, the wafer was annealed at 550°C for 5 min. I<sub>d</sub>-V<sub>d</sub> characteristics of the fabricated MOSFETs are shown in Fig. 4 and the corresponding  $I_{d}\mbox{-}V_{g}$ characteristics are shown in Fig. 5. It really works with the subthreshold slope of about 77mV/dec, close to the theoretical value. However, the MOSFET suffers large gate leakage current and small saturation current. The main reason is that Al gate electrode is not suitable for the process: during 550°C annealing, the HfO<sub>2</sub> film may be destroyed by Al while the doping in source/drain has not been fully activated. Substantial improvement of MOSFET performance can be expected if other suitable metal gate electrode, such as TiN, is used.

Fig. 4  $I_{ds}$ - $V_{ds}$  characteristics of an NMOSFET with ~ 4 nm ALD HfO<sub>2</sub> gate dielectric and 200 nm Al gate electrode. L/W = 5 $\mu$ m/400 $\mu$ m, V<sub>g</sub> from 0 to 1.0 V with a step of 0.25V.

Fig. 5 Corresponding  $I_{ds}$ - $V_{gs}$  characteristics at  $V_{ds} = 0.5$  and 1 V. The NMOSFET is as described in Fig. 4.

#### 3.3 ALD HfO<sub>2</sub> on Ge substrate

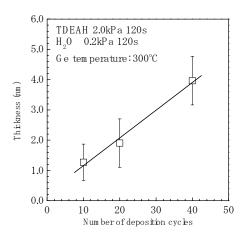

$\rm HfO_2$  film was deposited on Ge substrates using the above-mentioned ALD technology with almost the same process parameters. The dependence of  $\rm HfO_2$  thickness on cycle number is shown in Fig. 6. The film thickness is also extracted from ellipsometry measurement using a one-layer model simulation. The deposition rate is estimated to be 0.09 nm/cycle, close to the deposition rate on Si substrate.

Fig. 6 Dependence of  $HfO_2$  film thickness on number of deposition cycles for  $HfO_2$  deposition on Ge substrates at  $300^{\circ}C$ .

Figure 7 shows the high-resolution RBS profile of the HfO<sub>2</sub> deposited on Ge substrate. Based on the abovementioned interface definition, the thicknesses of HfO<sub>2</sub> film and interfacial layer are estimated to be 2.0 nm and 0.26 nm, respectively. The ratio of Hf and O is about 1:2 at the top layer, indicating that almost stoichiometric HfO<sub>2</sub> was deposited. However, we find that there exist Ge atoms in the top HfO<sub>2</sub> layer and Hf atoms in the interfacial layer with a relatively high content. It indicates both Ge and Hf diffusion may occur during ALD HfO<sub>2</sub> growth.

Fig. 7 High-resolution RBS profile of ALD  $HfO_2$  film deposited on Ge substrate for 40 cycles at 300°C.

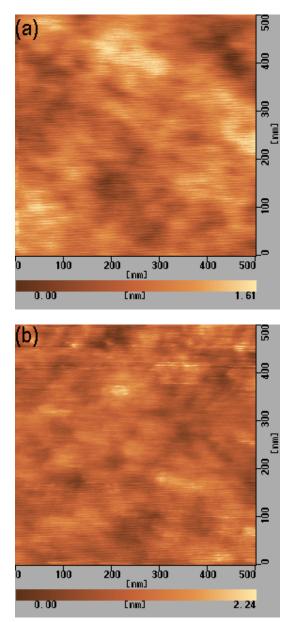

Fig. 8 shows a typical surface morphology measured by AFM on the DHF-treated Ge wafer before and after ALD. The roughness (rms) measured in a 500 nm  $\times$  500 nm area is approximately 0.27 nm before deposition and 0.30 nm after ALD deposition for 20 cycles. Based on the above observations, we propose that the ALD of HfO<sub>2</sub> on Ge surface still obeys layer-by-layer growth kinetics, similar to that on Si surface.

Fig. 8 AFM images of Ge surface (a) before (after DHF dipping) and (b) after 20 cycles of HfO<sub>2</sub> ALD at 300°C. The average surface roughness ( $R_a$ ) is determined to be approximately 0.27 nm and 0.30 nm respectively.

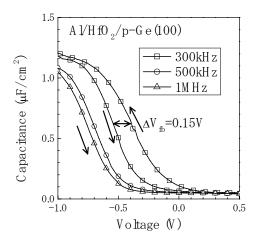

Figure 9 shows C-V characteristics of the Al/HfO<sub>2</sub>/p-Ge MIS capacitor. It exhibits a relatively large hysteresis, about 0.15V as measured at 300 kHz in both scanning directions. With increasing the measurement frequency, the C-V curve shifts to negative direction and the accumulation capacitance slightly decreases. These

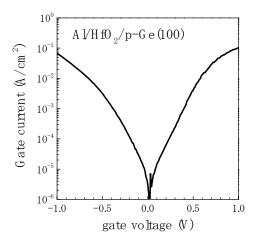

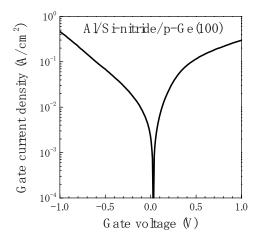

behaviors, i.e., frequency dependency and large hysteresis, are typical for Ge capacitance [10,11]. From the 300 kHz accumulation capacitance, EOT is estimated to be 2.5nm, close to that on Si substrate with the same deposition cycle number. Fig. 10 shows the gate leakage current of the Al/HfO<sub>2</sub>/p-Ge capacitor. The leakage current is large in both polarities, probably due to the small energy gap of Ge.

Fig. 9 Capacitance-voltage curves measured at 300, 500, and 1000 kHz for Al/HfO<sub>2</sub>/p-Ge(100) (MIS) capacitors. HfO<sub>2</sub> was deposited for 40 cycles at  $300^{\circ}$ C.

Fig. 10 Gate leakage current density of Al/HfO<sub>2</sub>/p-Ge(100) MIS capacitors. HfO<sub>2</sub> was deposited for 40 cycles at  $300^{\circ}$ C.

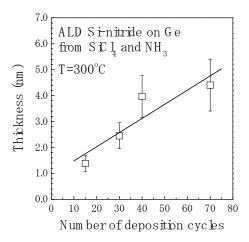

#### 3.4 ALD Si-nitride on Ge substrate

High quality Si-nitride thin film has been fabricated on Si by ALD using precursors of SiCl<sub>4</sub> and NH<sub>3</sub> [16] and high-performance MOSFETs with the ALD Sinitride or ALD Si-nitride/SiO<sub>2</sub> stack gate dielectrics have been demonstrated in our group [21-23]. In this work, Sinitride thin film was deposited on Ge substrate using the similar ALD process. The dependence of Si-nitride film thickness on cycle number is shown in Fig. 11. From the linear fitting, the deposition rate is estimated to be 0.055 nm/cycle. However, the linearity is not good. The deposition decreases with the film thickness increasing.

Fig. 11 Dependence of film thickness on number of deposition cycles for ALD Si-nitride on Ge substrates at  $300^{\circ}$ C from SiCl<sub>4</sub> and NH<sub>3</sub> as precursors.

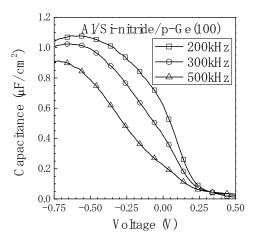

Al/Si-nitride/p-Ge MIS capacitors were fabricated using the above-mentioned process. The Si-nitride was deposited for 70 cycles at 350°C. The thickness measured from ellipsometry is about 3.9 nm. Fig. 12 shows C-V characteristics measured at 200, 300, and 500 kHz. The capacitance shows a large frequency dependency and large hysteresis, similar to the Al/HfO<sub>2</sub>/p-Ge capacitor. The EOT extracted from the 200 kHz accumulation capacitance is approximately 3.0 nm.

Fig. 12 Capacitance-voltage curves measured at 200, 300, and 500 kHz for Al/Si-nitride/p-Ge(100) (MIS) capacitors. Si-nitride was deposited for 70 cycles at 350°C, and the thickness measured from ellipsometry is about 3.9 nm.

The corresponding gate leakage current is shown in Fig. 13. It also suffers large leakage current, similar to the Al/HfO<sub>2</sub>/p-Ge capacitor. The poor quality of the high- $\kappa$  films deposited on Ge may correspond to the Ge surface itself, rather than the deposition process. If a

suitable Ge surface passivation process is carried out, the MIS quality may be improved. More studies are necessary before implement of Ge MOSFET.

Fig. 13 Gate leakage current density of Al/HfO<sub>2</sub>/p-Ge(100) MIS capacitors.

# 4. Conclusions

$HfO_2$  films were deposited by the alternate exposure of TDEAH and water on both Si and Ge substrates. In both cases, the deposited  $HfO_2$  is almost stoichiometic and the film growth is believed to follow a layer-by-layer growth kinetics without an incubation period because of the linear relationship between deposited film thickness and cycle number, as well as the smooth film surface. ALD  $HfO_2$  on Si exhibits good electrical properties, comparable to recently reported data [18-20]. MOSFETs with the ALD  $HfO_2$  gate dielectrics have been demonstrated using a simple one-mask fabrication process. Typical  $I_d$ - $V_d$  and  $I_d$ - $V_g$  characteristics have been observed.

ALD HfO<sub>2</sub> on Ge exhibits a relatively large hysteresis and frequency dependency in C-V characteristics and large gate leakage current. For comparison, ALD Si nitride on Ge suffers similar problems though high quality ALD Si-nitride film can be

fabricated on Si substrate. It indicates that the poor electrical properties of the Al/ALD high- $\kappa$ /Ge diodes may corresponds to the Ge surface itself, rather than the high- $\kappa$  deposition process. Nevertheless, stoichiometic HfO<sub>2</sub> can be deposited on Ge, whereas further studies are necessary to improve its quality.

## References

- [1] G. D. Wilk, et al., J. Appl. Phys. 89 (2001) 5243.

- [2] J. Aarik, et al., Thin Solid Films **340** (1999) 110.

- [3] K. Kukli, et al., J. Mater. Electron. 14 (2003) 361.

- [4] Y. S. Li, et al., Appl. Phys. Lett. 81 (2002) 2041.

- [5] S. Kamiyama, et al., Appl. Phys. Lett. 87 (2005) 132904.

- [6] P. D. Kirsch, et al. J. Appl. Phys. 99 (2006) 023508.

- [7] S. Hino, et al., Jpn. J. Appl. Phys. 42 (2003) 6015.

- [8] Y. Yokoyama, et al., Jpn. J. Appl. Phys. 45 (2006) 7091.

- [9] J. J. Rosenberg, et al., IEEE Electron Device Lett., 9 (1988) 639.

- [10] C. O. Chui, et al., IEDM Tech. Dig. (2002) 437.

- [11] C. H. Huang, et al., IEDM Tech. Dig. (2003) 319.

- [12] A. Ritenour, et al., IEDM Tech. Dig. (2003) 433.

- [13] S. Zhu, et al., IEEE Electron Device Lett., 26 (2005) 81.

- [14] D. S. Yu, et al., IEEE Electron Device Lett., 26 (2005) 118.

- [15] S. C. Martin, et al., IEEE Electron Device Lett., 10 (1989) 325.

- [16] A. Nakajima, et al., Appl. Phys. Lett., 79 (2001) 665.

- [17] J. Wang, et al., J. Mater. Sci. 27 (1992) 5397.

- [18] J. Niinisto, et al., J. Mater. Chem. 15 (2005) 2271.

- [19] K. Kukli, et al., J. Electrochem. Soc. 151 (2004) F-189.

- [20] M. Cho, et al., Appl. Phys. Lett. 83 (2003) 5503.

- [21] A. Nakajima, et al., J. Vac. Sci. & Techn. B, 20 (2002) 1406.

- [22] A. Nakajima, et al., Microelectron. Reliability 42 (2002) 1823.

- [23] A. Nakajima, et al., Jpn. J. Appl. Phys., 44 (2005) L903.